# THE TECHNICAL UNIVERSITY OF ŁÓDŹ Faculty of Electrical and Electronic Engineering

Master of Engineering Thesis

## DESIGN OF RADIATION TOLERANT TRANSMISSION CHANNEL CIRCUIT

Jakub Mielczarek

Student's number: 106119

Supervisor: Grzegorz Jabłoński, PhD

Auxiliary supervisor: **Dariusz Makowski, MSc**

Łódź, 2005

| 1          | INTRODUCTION                                                                               | 5   |  |  |  |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|

| 2          | OBJECTIVE OF THE THESIS                                                                    | 7   |  |  |  |  |  |  |  |

| 2.1        | PROBLEM DESCRIPTION                                                                        | 7   |  |  |  |  |  |  |  |

| 2.2        | PROPOSED SOLUTION                                                                          |     |  |  |  |  |  |  |  |

| 2.3        | POSSIBLE IMPLEMENTATIONS                                                                   |     |  |  |  |  |  |  |  |

| 3          | RADIATION EFFECTS ON ELECTRONIC DEVICES                                                    | 12  |  |  |  |  |  |  |  |

| 3.1        | NEUTRON RADIATION                                                                          |     |  |  |  |  |  |  |  |

|            | 3.1.1         Firm Errors           3.1.2         Soft Errors                              |     |  |  |  |  |  |  |  |

| 3.2        | GAMMA RADIATION                                                                            |     |  |  |  |  |  |  |  |

| 4          | FAMILIES OF FPGA DEVICES, MICROCONTROLLERS AND THEIR RADIATION<br>TOLERANCE                |     |  |  |  |  |  |  |  |

| 4.1        | SRAM Based FPGA                                                                            |     |  |  |  |  |  |  |  |

| 4.1        | FLASH-BASED FPGA                                                                           |     |  |  |  |  |  |  |  |

| 4.3        | ANTIFUSE FPGA                                                                              | 20  |  |  |  |  |  |  |  |

| 4.4        | RADIATION HARDENED, RADIATION TOLERANT FPGA                                                |     |  |  |  |  |  |  |  |

| 4.5<br>4.6 | MICROCONTROLLERS<br>Radiation Induced Errors in Finite State Machines and Microcontrollers |     |  |  |  |  |  |  |  |

| 4.7        | SELECTION OF THE OPTIMAL DEVICE                                                            |     |  |  |  |  |  |  |  |

| 5          | RADIATION HARDENING AND MITIGATION TECHNIQUES                                              | 24  |  |  |  |  |  |  |  |

| 5.1        | TECHNOLOGICAL HARDENING AND MITIGATION                                                     |     |  |  |  |  |  |  |  |

| 5.2        | DOUBLE MODULAR REDUNDANCY, TRIPLE MODULAR REDUNDANCY.                                      |     |  |  |  |  |  |  |  |

| 5.3<br>5.4 | HAMMING CODES                                                                              |     |  |  |  |  |  |  |  |

| 5.5        | SCRUBBING                                                                                  |     |  |  |  |  |  |  |  |

| 6          | PROJECT DESCRIPTION                                                                        | 35  |  |  |  |  |  |  |  |

| 6.1        | OVERVIEW                                                                                   |     |  |  |  |  |  |  |  |

| 6.2        | RADIATION TOLERANT MCU BASED ON PIC16C57                                                   |     |  |  |  |  |  |  |  |

|            | <ul> <li>6.2.2 Techniques Employed for SEU Mitigation</li></ul>                            |     |  |  |  |  |  |  |  |

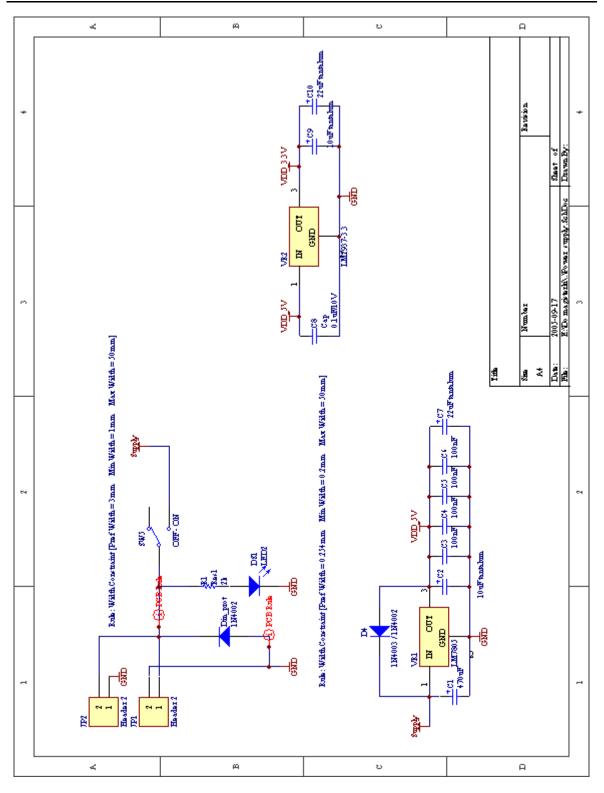

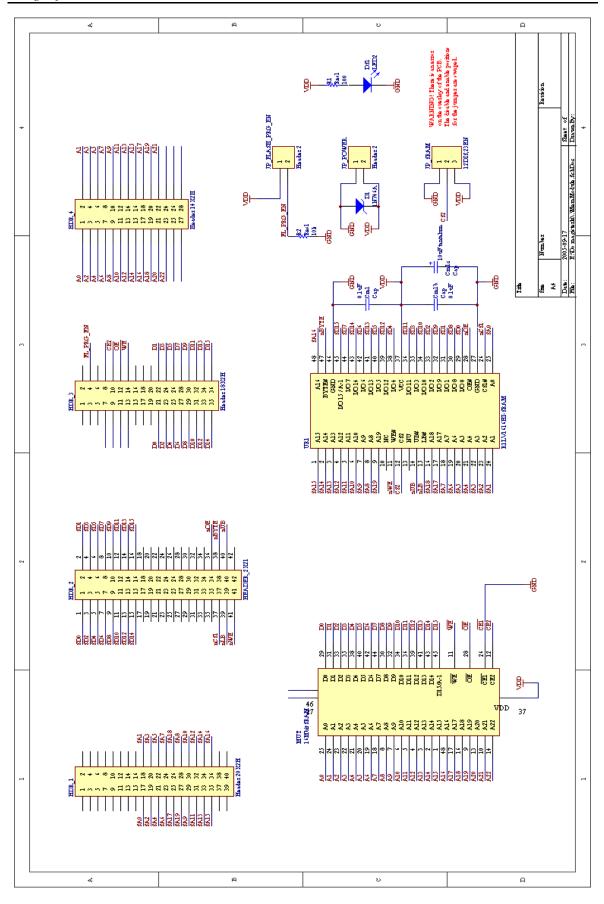

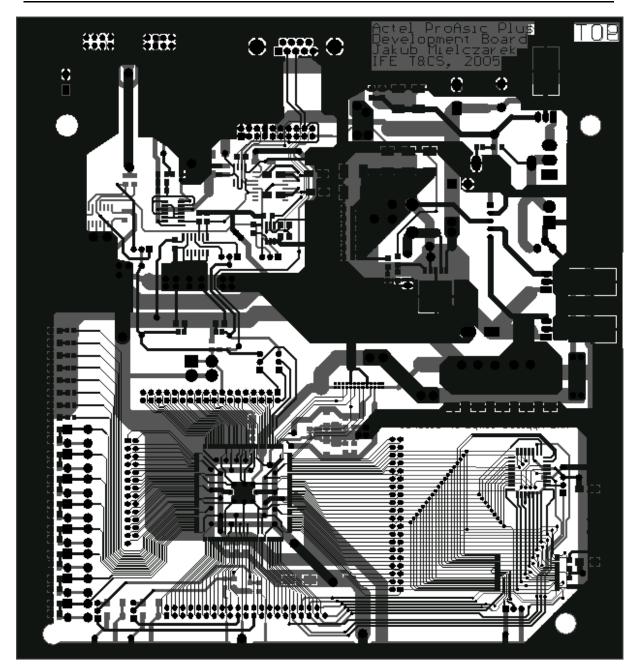

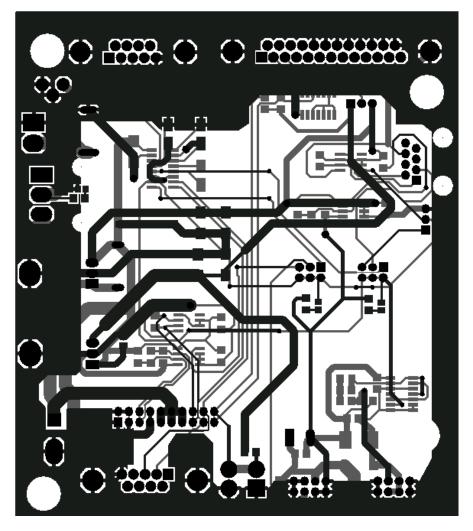

| 6.3        | HARDWARE PLATFORM                                                                          |     |  |  |  |  |  |  |  |

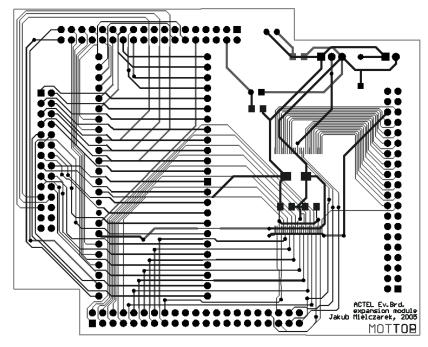

|            | 6.3.1 FPGA Development Board                                                               |     |  |  |  |  |  |  |  |

| 6.4        | 6.3.2 Transceiver                                                                          |     |  |  |  |  |  |  |  |

| 0.4        | EXEMPLARY APPLICATION – SRAM SEU DETECTOR                                                  |     |  |  |  |  |  |  |  |

|            | 6.4.3       Software for PC                                                                |     |  |  |  |  |  |  |  |

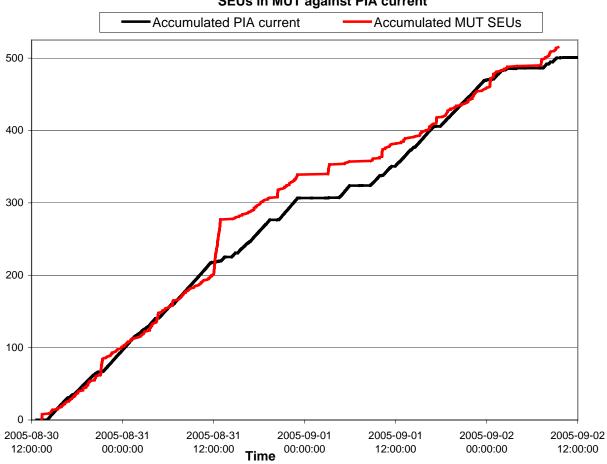

| 7          | EXPERIMENTAL RESULTS FROM DEUTSCHES ELEKTRONEN-SYNCHROTRON                                 | 85  |  |  |  |  |  |  |  |

| 8          | CONCLUSIONS                                                                                | 98  |  |  |  |  |  |  |  |

| REF        | ERENCES 1                                                                                  | 100 |  |  |  |  |  |  |  |

| APP        | ENDIX A SCHEMATICS AND PCB LAYOUTS 1                                                       | 103 |  |  |  |  |  |  |  |

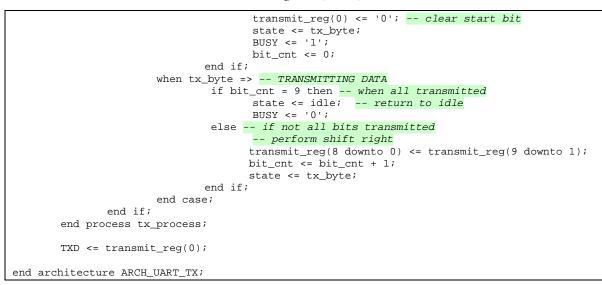

| APP        | ENDIX B EXAMPLES OF VHDL CODE 1                                                            | 115 |  |  |  |  |  |  |  |

| APP        | ENDIX C SUMMARY OF DETECTED SEUS 1                                                         | 28  |  |  |  |  |  |  |  |

### Streszczenie

Niniejsza praca magisterska została wykonana dzięki współpracy Politechniki Łódzkiej z ośrodkiem Deutsches Elektronen-Synchrotron (DESY) w ramach programu Coordinated Accelerator Research in Europe (CARE). Ośrodek ten mieści się w Hamburgu, w Niemczech. DESY specjalizuje się w badaniach dotyczących fizyki wysokich energii i cząstek elementarnych. Mieszczą się tam również laboratoria biologii molekularnej, chemii i materiałoznawstwa, wykorzystujące w badaniach promieniowanie synchrotronowe. Ośrodek DESY został wybrany jako lokalizacja nowej generacji akceleratora cząstek. International Linear Collider (ILC) jest konstruowany i budowany w ramach międzynarodowej współpracy ośrodków badawczych i naukowych. Akcelerator ten umożliwi przyspieszanie elektronów i pozytonów do energii rzędu 1 TeV. Będzie to możliwe dzięki zastosowaniu niedawno opracowanej i jeszcze testowanej technologii Teraelectronvolt Superconducting Linear Accelerator (TESLA). Technologia ta opiera się na nadprzewodzacych wnękach rezonansowych wykonanych z czystego niobu. Fala elektromagnetyczna o częstotliwości 1,3 GHz przyspiesza elektrony i pozytony. W końcowym etapie przyspieszania cząstki są poddawane kolizji. Produkty kolizji być może pozwola na zweryfikowanie istnienia bozonu Higssa. Strumień wysokoenergetycznych elektronów posłuży również jako źródło promieniowania w laserze rentgenowskim X-Ray Free Electron Laser (X-FEL). To źródło koherentnego promieniowania rentgenowskiego będzie w stanie wytwarzać impulsy o czasie trwania rzędu 80 femtosekund, pozwalając na obserwację m.in. drgań struktur krystalicznych czy kolejnych etapów podczas zachodzenia reakcji chemicznych.

Akcelerator ILC będzie kontrolowany przez zaawansowane, głównie cyfrowe, systemy sterowania. Systemy te oparte zostaną o urządzenia programowalne FPGA i procesory sygnałowe DSP. Akcelerator został zaprojektowany z wykorzystaniem tylko jednego tunelu. Będzie on mieścił zarówno tor przyspieszający wykonany ze wspomnianych wnęk rezonansowych, jak i wymienione systemy sterowania. Takie rozwiązanie sprawi, iż urządzenia elektroniczne będą narażone na wpływ szkodliwego promieniowania gamma i neutronów. Wynikiem tego mogą być awarie urządzeń elektronicznych, polegające m.in. na nieprzewidywalnych zatrzymaniach pracy modułów, ich funkcjonowaniu w sposób niezgodny z zaprogramowanym lub trwałe uszkodzenia tychże urządzeń. Dlatego też, ważnym aspektem projektu ILC jest ilościowe zbadanie

i opisanie potencjalnych, negatywnych skutków wpływu promieniowania gamma i neutronów na urządzenia elektroniczne. Co więcej, konieczne jest opracowanie sposobów łagodzenia tychże skutków lub zapobiegania im.

Część praktyczna wykonana w ramach niniejszej pracy magisterskiej koncentruje się na zaprojektowaniu i wykonaniu niezawodnego, niewrażliwego na pewne promieniowania neutronowego, układu cyfrowego. Głównym skutki zadaniem powyższego układu jest umożliwienie i obsługa niezawodnej komunikacji pomiędzy różnymi urządzeniami elektronicznymi, znajdującymi się w tunelu akceleratora, a centralnym systemem, znajdującym się poza wpływem promieniowania. Potrzeba opisanej komunikacji rodzi się z dwóch powodów: konieczności poddania urządzeń elektronicznych testom w środowisku promieniowania gamma i neutronowego, oraz monitorowania poziomu promieniowania w tunelu akceleratora. Układ został zaprojektowany, wykonany, uruchomiony i poddany testom w tunelu akceleratora LINAC II w ośrodku DESY. Testy odbyły się na przełomie sierpnia i września 2005 roku. Na projekt układu złożyło się wiele etapów. Praca zawiera opis każdego z nich. Przed przystąpieniem do fazy projektowania, przestudiowano wpływ promieniowania gamma i neutronów na układy elektroniczne. Następnie przeprowadzono analizę dostępnych układów programowalnych pod kątem wrażliwości na promieniowanie, kosztów i możliwości wielokrotnego programowania. Do implementacji układu niewrażliwego na promieniowanie wybrano układ programowalny FPGA oparty na wbudowanej pamięci Flash. W układzie FPGA został zaimplementowany mikrokontroler oparty o rdzeń procesora PIC16C57, który jest szeroko wspieranym standardem. Do opisu układu cyfrowego użyto języka VHDL. Na część praktyczną pracy złożyło się kilka etapów. Pierwszym było zaprojektowanie i zmontowanie płytek drukowanych. Kolejnym, wspomniany opis układu w języku VHDL. Ostatnim etapem było napisanie oprogramowania na zaimplementowany mikrokontroler. Dzięki temu oprogramowaniu, wykonane urządzenie może funkcjonować jako detektor zjawisk Single Event Upset (SEU) w pamięci SRAM. Detektor taki może zostać wykorzystany w zautomatyzowanym systemie pomiaru strumienia neutronów w tunelu akceleratora. Dodatkowo powstało oprogramowanie na komputer PC, pozwalające na przetestowanie wykonanego urządzenia, podczas gdy pełniło ono wspomnianą funkcję detektora. Podczas 72-godzinnego testu urządzenie niezawodnie pracowało w obecności promieniowania gamma i neutronowego. W tym czasie bezbłędnie realizowało zaprogramowaną funkcję

detektora SEU w pamięci SRAM. Komunikacja z komputerem PC, umieszczonym poza tunelem akceleratora przebiegała również bezbłędnie.

Mikrokontroler zaimplementowany w układzie FPGA został częściowo uodporniony na promieniowanie wyłącznie na poziomie języka VHDL. Do tego celu zostały użyte kody Hamminga i potrójna redundancja. Metoda uodparniania oparta na potrójnej redundancji została sformalizowana w postaci algorytmu. Pozwala ona na rozdzielenie procesu opisu układu cyfrowego od procesu uodpornienia na wpływ promieniowania neutronowego. Dzięki temu nie jest wymagana ingerencja w kod źródłowy VHDL. Ograniczeniem opracowanej metody jest wsparcie wyłącznie dla układów FPGA ProAsic Plus firmy Actel. Dalsze badania są niezbędne, aby zweryfikować jej realizowalność dla innych rodzajów układów FPGA.

# 1 Introduction

The present master's thesis was carried out in cooperation with Deutsches Elektronen-Synchrotron (DESY). DESY is a high-energy particle physics research centre, located in Hamburg, Germany. It also incorporates molecular biology and chemistry laboratories, taking advantage of synchrotron radiation. The centre has been chosen as a home site for a new generation particle collider, which will be designed and built in an international collaboration. The International Linear Collider (ILC) will accelerate electrons and positrons to energies of up to 1 TeV. The capability will be enabled by the newest, currently being tested in TESLA Test Facility 2 (TTF2) site in DESY, Tera Electronvolt Superconducting Linear Accelerator (TESLA) technology. In this technology, pure niobium, superconducting cavities fed with 1.3 GHz electromagnetic wave accelerate the electrons and positrons, bringing them into collisions. The products of collisions might verify the existence of the Higgs' particle, being considered the origin of matter's mass. The highly energetic streams of electrons will be also the basis for X-Ray Free Electron Laser (X-FEL). This coherent source of ca. 80-femtosecond X-ray pulses of high brilliance will facilitate the observation of crystalline structure oscillations and give empirical insight into subsequent steps of chemical reactions.

The ILC will be controlled by sophisticated, mostly digital, electronic control systems. The systems will be based on Field Programmable Gate Array (FPGA) devices, and Digital Signal Processors (DSPs). Since the main accelerator tunnel will confine both the accelerating cavities and the electronic control systems, the latter will be exposed to influence of mixed neutron and *Bremsstrahlung* gamma radiation. Both constituents of the mixed radiation have detrimental effects on electronic devices, ranging from inducing halts or infinite loops, functional interrupts to severe, permanent damage. The effects may be short or long term ones. Therefore, it is vital for the ILC project to quantify the damage effects and take measures against them.

This project concentrates on designing and implementing a reliable, radiation tolerant transmission channel circuit, enabling flexible and reliable communication between electronic devices located in the accelerator tunnel and central system located in radiation-free environment. The need of such communication channel arises from two necessities: testing electronic devices in the accelerator's radiation environment, monitoring neutron and/or gamma radiation level in the accelerator tunnel. The detailed

requirements for the radiation tolerant device and its exemplary application are described in Chapter 2.

Before the design phase commenced, the influence of neutron and gamma radiation on electronic devices was thoroughly studied. The summary of the study can be found in Chapter 3.

The assumption was made, that the transmission channel circuit should be built based on Commercial Off-The-Shelf (COTS) components only. Therefore, as documented in Chapter 4, various families of suitable electronic devices were considered for the implementation and the optimal one has been chosen.

Investigation of already developed and well-tested techniques improving radiation tolerance of digital systems was carried out. The most valuable techniques are described in Chapter 5.

The transmission channel circuit was described in Very High Speed Integrated Circuit Hardware Description Language (VHDL) and implemented in a Flash-based FPGA device. The circuit is based on industry standard PIC16C57 CPU. Some of the mitigation techniques described in Chapter 5 were implemented to improve the radiation tolerance of the transmission channel circuit. During this process a semi-automatic technique for mitigating sequential designs on the VHDL level was developed and used in the project. A printed circuit board was designed and assembled to facilitate prototyping of the circuit. The board, together with designed and assembled auxiliary hardware was used during in-field tests. Finally, software for the CPU was developed, to demonstrate device's capabilities and test it in field. Chapter 6 gives the full description of the project.

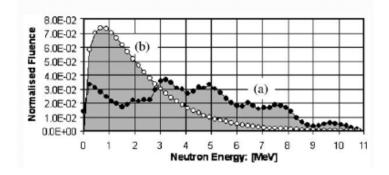

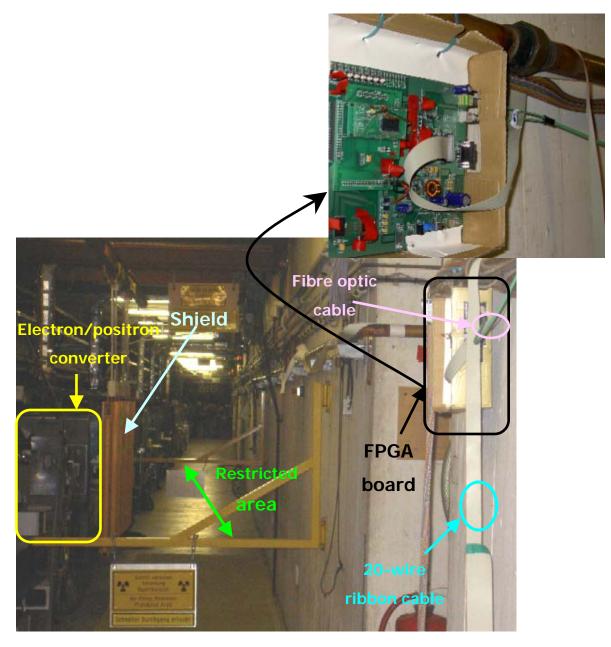

The physically implemented transmission channel circuit, together with auxiliary hardware was subject to tests in DESY, in August and September 2005. The radiation tolerant device was installed in LINAC II accelerator, whose radiation environment is harsher than that of TTF2 and the planned ILC. The device was placed in close vicinity of the *electron-to-positron* converter, guaranteeing high doses of the mixed radiation reaching the device. Description of experiments, which were carried out and the obtained results are presented in Chapter 7.

# 2 Objective of the Thesis

The aim of this master's thesis is to design a radiation tolerant device, which will enable reliable exchange of information between accelerator tunnel and a monitoring station (e.g. personal computer) located outside the tunnel. Operation of the device will be demonstrated in a useful application.

This chapter gives details on the origins of the necessity of such design, and briefly describes the main idea behind the solution.

## 2.1 Problem Description

The International Linear Collider (ILC) tunnel will house both array of superconducting accelerating cavities and sophisticated electronic control systems (mainly digital), responsible for controlling the collider. Such an arrangement exposes the electronic systems to mixed gamma radiation and neutron influence, of doses and intensities greater by orders of magnitude than that occurring in regular conditions. Therefore measures need to be taken to harden electronic devices against radiation, neutralize or mitigate its negative effects. Moreover, the points of failure, due to radiation, of the systems must be identified and evaluated. For that purpose a reliable communication channel must exist between devices under test, located in the accelerator tunnel, and a monitoring station, installed outside the tunnel, e.g. in the accelerator hall.

## 2.2 Proposed Solution

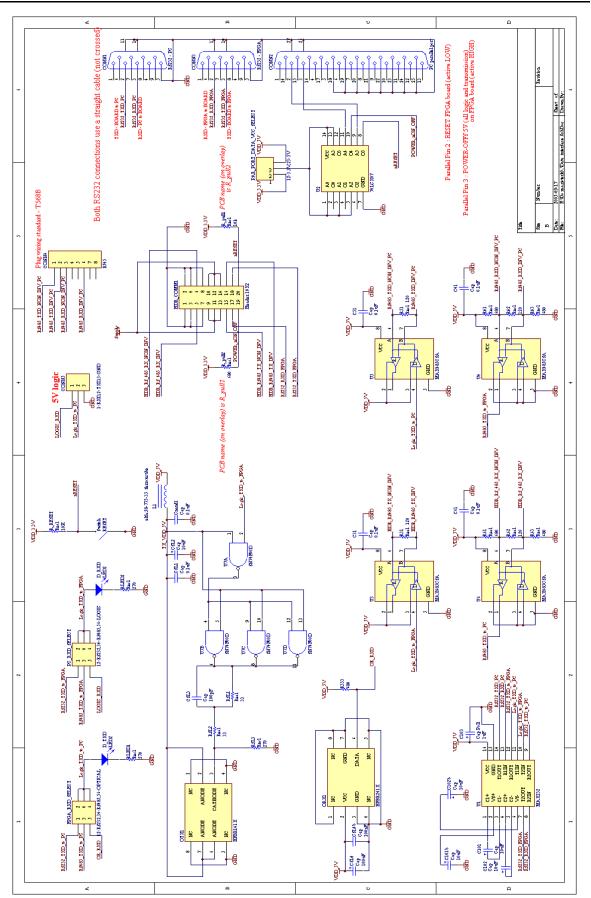

Communication channel in the accelerator environment will be subject to the mixed radiation and electromagnetic interference from high-power klystrons, electric vacuum pumps and nearly omnipresent control electronics (see Figure 2.1).

c)

Figure 2.1. Service hall of LINAC II accelerator.

a) Array of high-power klystrons; b) Control electronics;

c) High-power waveguide with SLED (SLAC Energy Doubler);

d) Vacuum pump

d)

Thus, a reliable channel must meet following requirements:

- Transmission channel circuit hardened against radiation or radiation tolerant,

- Transmission medium immune to electromagnetic interference (EMI).

The transmission medium does not need to be radiation protected, as neither gamma rays nor neutrons generate Single Event Effects (SEE – see section 3.1) in known media. The only observed degradation of medium under gamma radiation is described in section 3.2.

Apart from the above requirements, the channel must enable the following:

- Full-duplex serial communication between monitoring station and transmission channel circuit - serial communication reduces the number of necessary signal lines,

- Set of basic control signals (reset, power-off) for the transmission circuit and/or the device under test. The channel circuit may provide those signals for the Device Under Test (DUT), or the lines may be shared, thus reducing the number of control lines,

- Deliver power to the communication circuit and the DUT from power supply located outside the accelerator tunnel.

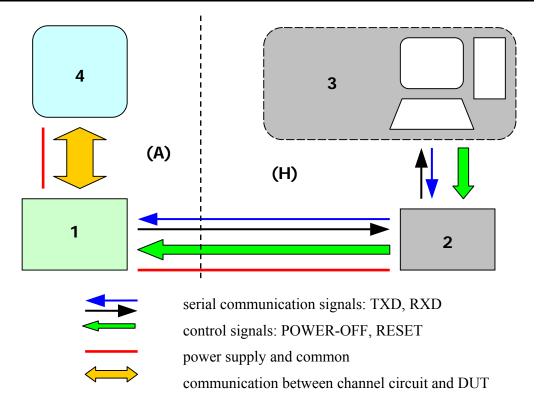

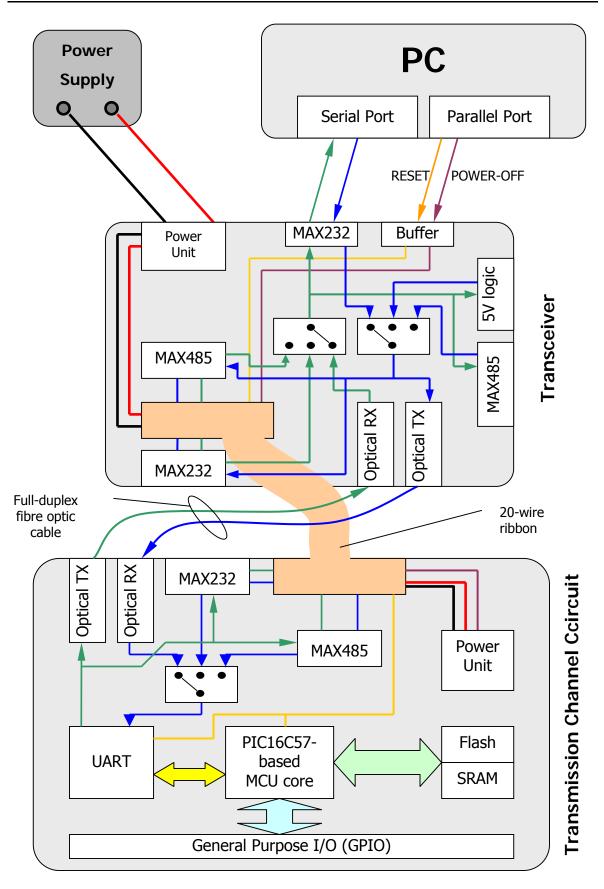

The most valuable solutions are universal ones, allowing easy accommodation to new conditions. To make this requirement and the ones mentioned above feasible, a transceiver, in a broad sense, is needed on the side of the monitoring station. The transceiver should interface common communication media and standards supporting serial communication, pass control signals from monitoring station and deliver power to the devices in tunnel. The general block diagram of proposed communication channel set-up is presented in Figure 2.2.

Figure 2.2. Block diagram of proposed communication channel. 1 – radiation hardened or tolerant communication circuit, 2 – communication, control signal and supply transceiver, 3 – monitoring station, 4 –DUT, (A) - accelerator tunnel, (H) - accelerator hall. The power supply unit is not included.

#### 2.3 Possible Implementations

The proposed block diagram in Figure 2.2 is a high-level abstraction of the design. Choice has to be made on the components used for implementing it. To make the devices easy to build, commercial off-the-shelf (COTS) components will be used. This lowers the cost, and enables to avoid problems arising from limited components availability.

The transmission channel circuit should be flexible enough, to interface it to various devices, with only minor or no changes to the circuit's configuration. It is not acceptable, that for every type of device to be interfaced, a different circuit must be built, starting from the schematic and printed circuit board level. This would increase the cost of a single device significantly, and extend design time a number of times. The circuit should be also able to accommodate different signalling standards and protocols. The design, which will meet the requirements, calls for a programmable or re-programmable transmission channel circuit. Programmability or re-programmability is available in many COTS component families, just to mention re-programmable

integrated circuits like: GAL. PLD. and FPGA devices. microprocessors, and microcontrollers. In this particular design, however, **FPGA** devices and microcontrollers are the field of interest. Both provide abundant resources, thus greatly lowering the number of required components and decreasing the complexity of design on the PCB level.

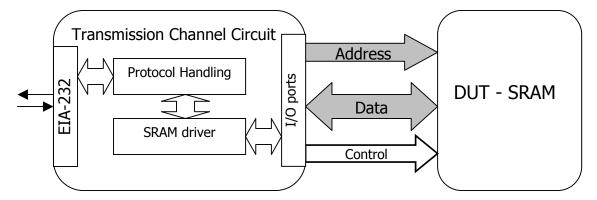

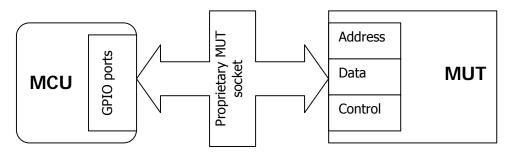

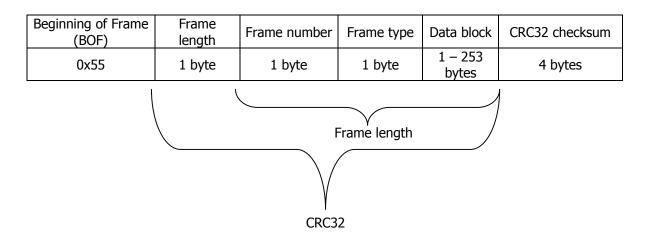

The channel circuit must be a command driven system, with a degree of autonomy. It should support a well-established serial communication protocol. The EIA-232 protocol is sufficient as a carrier, for a more reliable, frame-based protocol. The possibility of employing signalling standard other than EIA-232 should be also available. There must exist a means of guaranteeing reliability of communication, e.g. through Cyclic Redundancy Check (CRC). The types of devices, which can be interfaced to the transmission channel circuit, may not depend on circuit's architecture, should be handled in a general Input/Output manner. The main task for the circuit will be testing of electronic devices in the radiation environment. The core functions for this, such as proper communication with a DUT through control signals and buses should be implemented in the channel circuit, not the monitoring station. Simple, but extremely useful, application for the circuit could be detector of Single Event Upsets (SEUs - see section 3.1.2) in a Static Random Access Memory (SRAM). In this case the DUT would be the SRAM. The memory would be tested for occurrence of SEUs. The task for the channel circuit would be writing and reading the memory, accomplished through proper use of chip's address and data buses, accompanied by assertion of control signals. The block diagram of such application is shown in Figure 2.3. The number of available I/Os must be sufficient for a wide range of SRAM modules, i.e. 8 I/Os for data bus, at least 20 I/Os for address (1 MB address space), at least one I/O for Chip Select (CS), one for Write Enable (WE) and one for Output Enable (OE). This gives a total of at least 31 I/O lines.

Figure 2.3. Block diagram of an exemplary application of the transmission channel circuit

# 3 Radiation Effects on Electronic Devices

This chapter briefly describes the adverse effects of neutron and gamma radiation on electronic devices and optical components. The emphasis is put on soft errors, particularly Single Event Upsets (SEUs), since the main goal of this project is to minimize their effects.

## 3.1 Neutron Radiation

The detrimental neutron radiation is the dominating component of accelerator's radiation environment. Electronic devices operating under neutron irradiation suffer damage. The damage can be done through different mechanisms. They are the displacement damage and Single Event Effects (SEEs).

Since neutrons have no electronic charge, they cannot interact with semiconductor material atoms electrically. However, being 1840 times heavier than an electron, they interact with semiconductor lattice atoms through collisions. The collisions result in dislodging or displacing the lattice atoms from their lattice sites. The atoms are forced to take up interstitial positions within the crystal, resulting in distortion of lattice structure. This effect, as being of mechanical nature, is significant due to high-energy neutrons, such as cosmic ones, thus being a serious problem in space applications. Among results of the damage are resistivity changes and bipolar transistor gain degradation [1]. The displacement damage may have reversible nature. The semiconductor lattice structure may be restored. This self-healing of a device is referred to as annealing. It relies on thermal motion of the defects. The displaced atoms migrate from interstitial to vacancy positions. On the other hand, the migrating atoms may form stable associations with impurity atoms in the semiconductor structure. This will enhance the degradation, as such associations are defects in the lattice.

The second type of neutron effect on electronic systems is an indirect one. As mentioned earlier, there are no direct electrical interactions of neutrons with semiconductor atoms. Nevertheless, neutrons can induce ionisation through secondary processes [1]. The most important in the context of this project is the generation of alpha particles within semiconductor lattice. Low-energy neutrons, in particular *thermal neutrons*, dominate the neutron-energy-spectrum of the electron accelerator housed in a concrete containment. Under such conditions the neutron capture reaction in Boron

(<sup>10</sup>B) atoms, present in silicon chips as dopant and used in passivation layers, takes place. The product of the reaction can be either <sup>7</sup>Li ion or <sup>4</sup>He ion. The <sup>4</sup>He ion (an alpha particle) is probably the agent for triggering SEE in silicon devices [2]. Alpha particles also emanate from heavy elements, contaminants of chip package material, being potential sources of SEEs in commercial electronics. Such problems are avoided, by proper passivation of semiconductor structures. Unfortunately, this protection is ineffective in case of neutron-induced alpha particles, since they are generated in the very bulk of silicon.

The Single Event Effects are further subdivided into *firm* and *soft* errors, briefly characterized in sections 3.1.1 and 3.1.2.

#### 3.1.1 Firm Errors

The firm errors may result in permanent damage to the electronic device, rendering a device or its component unusable, posing potential threat to other system's components. The most popular firm error is Single Event Latch-up.

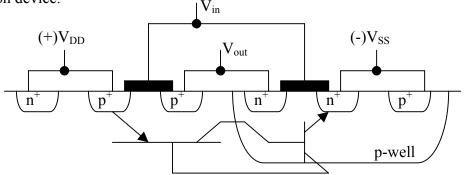

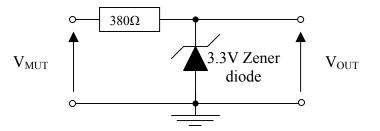

**Single Event Latch-up** takes place when parasitic thyristor in CMOS device (Figure 3.1) is switched into low-impedance ("on") state. The transition into "on" state is initiated by a charged particle (e.g. alpha particle) depositing charge in the structure, thus creating a current pulse. The current pulse switches the thyristor into conducting state and causes excessive current flow between power terminals through the device. If the power is not immediately switched off, the excessive heat can permanently damage the silicon device.

#### Figure 3.1. Parasitic thyristor in CMOS inverter structure (p-well technology) [3]

The other two known firm errors due to SEE consider power devices. The SEGR (Single Event Gate Rupture) and SEB (Single Event Burnout) are effects, which lead to the permanent damage of power MOSFET transistors. Since susceptibility to firm errors can be improved on technological level only, these phenomena are not described in detail.

#### 3.1.2 Soft Errors

The soft errors are much less severe than the firm ones. There is no direct permanent damage done to silicon devices due to soft SEE. The only impairment caused, is on the functional and performance level of the subject system. Digital systems are exposed to two types of soft errors in the radiation environment. These are Single Event Upset (SEU) and Single Event Transient (SET).

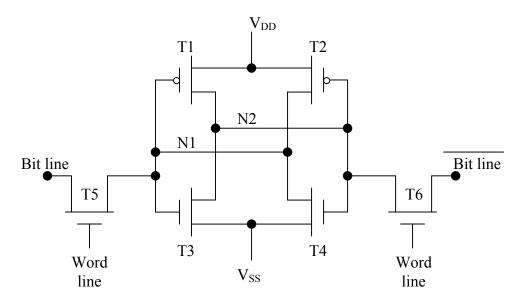

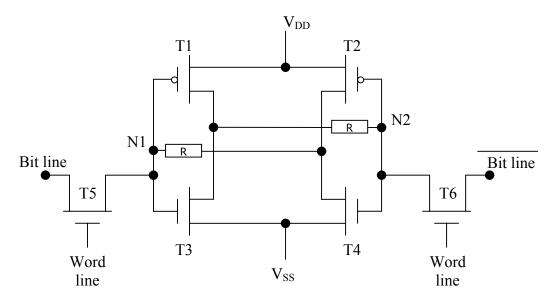

**Single Event Upset (SEU)** concerns data storage elements. Memory cells such as Static Random Access Memory (SRAM), Dynamic Random Access Memory (DRAM) and Master-Slave edge-triggered Flip-Flops are subject to this detrimental phenomenon. The effect of SEU is distortion of data stored in the cell, simply called a bit-flip. The bit-flip takes place if either logic '1' was written into the cell, but a logic '0' is read, or '0' was written and '1' is read. The mechanism of SEU is briefly explained for the 6-transistor SRAM cell shown in Figure 3.2 [3]. The cell consists of two cross-coupled CMOS inverters (T1-T3 and T2-T4) with access transistors (T5, T6) added.

Figure 3.2. The 6-transistor SRAM memory cell. T5 and T6 are n-type access transistors, T1 and T2 are p-type load transistors, T3 and T4 are n-type drive transistors [3].

The bit-flip in the cell of Figure 3.2 may proceed in two different scenarios, depending on the data, which is stored in the cell. If a '1' is stored, the transistors T2 and T3 are conducting ("on") whereas T1 and T4 are non-conducting "off". If an ionising particle, such as previously mentioned alpha particle, crosses the transistor's T4 or T1 channel region, it may ionise the area. This creates electron-hole pairs and may switch the affected

transistor into the "on" state, temporarily. If this happens, a low-voltage spike at node N2 is created. The '0' spike is propagated to the input of T1-T3 inverter and effectively latched into the cell. The scenario for the '0'-to-'1' bit-flip is similar. The difference is that in this case the vulnerable transistors are the T2 and T3. None of the "on" transistors can be switched "off" by ionisation.

Apart from impairing the data stored by a system or system's state, the SEU can temporarily transform system's functionality. This is a severe problem of SRAM based Field Programmable Gate Array (FPGA) devices (briefly characterized in section 4.1). Such an event is referred to as Single Event Functional Interrupt (SEFI). The rate at which SEU occur depends strongly on the packing density and fabrication technology of the affected integrated circuit. The higher the packing density is, the greater is the SEU rate. The feature size of circuit's fabrication technology is also an important factor. As scaling down progresses, the vulnerable area decreases. However, the supply voltage is usually also decreased and the frequency of operation rises. These effects, when cumulated, yield increased SEU sensitivity of sequential systems.

**Single Event Transient** affects combinatorial circuits only. It manifests itself by transient changes of voltage levels on signal lines, either being input to combinatorial blocks, or the outputs from them. An SET occurs if e.g. a block is driving an output in the logic '1' state, and a transient '0' is observed, which does not correspond to input vector. The SETs are mainly caused by ionising particles, particularly heavy ions. If an SET is latched in a storage element, it may be perceived as SEU.

## 3.2 Gamma Radiation

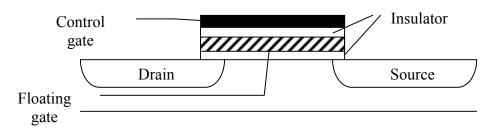

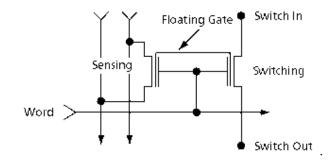

Gamma radiation is the high-energy electromagnetic radiation. The wavelength of high-energy gamma rays is of the order of fractions of an angstrom, i.e. of the order  $10^{-8}$  cm. Their interaction with matter is through three types of phenomena: the photoelectric effect, the Compton effect and pair creation. The damage caused by gamma radiation is ionisation damage [1]. Its level is determined by the Total Ionising Dose (TID) – the dose of ionising energy absorbed by the subject material – and the material type. Among the effects of gamma on electronic devices and structures, is the erasure of Flash memories. Flash memory is based on floating-gate MOSFET transistors, shown in Figure 3.3 [3]. The transistors act as non-volatile storage cells.

#### Figure 3.3. Floating-gate MOSFET transistor [3]

The memory cell is in programmed state (stores logic '1'), when charge is accumulated in the floating gate. When the programmed structure is exposed to gamma irradiation of high TID, the accumulated charge is gradually liberated from the floating gate, finally resulting in erasure of stored data, as confirmed experimentally [4]. Since gamma radiation is electromagnetic wave, it can be relatively easily shielded, by means of iron or lead slabs of proper thickness [1]. Other materials composed of elements of high "Z" (atomic) number may also be used for the purpose.

Gamma radiation causes also detrimental effects in optical devices. Current experimental results show limited tolerance of COTS (Commercial-Off-The-Shelf) optical components to gamma irradiation [5], [6]. The effects comprise reduction of LED transmitter efficiency and decreased SNR (Signal-To-Noise Ratio) at the P-I-N receiver [6]. Vulnerable element of optical component assemblies is the optical lens, which purpose is to increase the coupling efficiency of light into the fibre. The lens tends to lose clarity at high radiation doses. While the latter effect is a permanent one, the decrease of SNR is reversible if radiation is removed. Apart from the transducers, the optical fibre is also affected

by the gamma radiation [7]. The optical fibre suffers increase of attenuation per length unit, proportional to the TID. This effect is less significant if the fibre is "live", i.e. if it is intensively used. A fibre, which was subject to gamma radiation, will gradually self-heal provided it is used intensively while radiation is removed. This effect is referred to as *photobleaching*.

# 4 Families of FPGA Devices, Microcontrollers and Their Radiation Tolerance

This chapter gives a brief insight into families of FPGA devices available on the market. Microcontrollers are also briefly described. Every device family is characterized in respect of its re-programmability and radiation vulnerability. Finally radiation influence on Finite State Machines and microcontrollers is explained, and the choice of the device for the main component of the transmission channel circuit is justified.

Considering FPGA devices as candidates for the main component has its additional explanation in the fact, that these circuits will be broadly used in the control systems of the ILC. Engineers have recently completed and tested a prototype of cavity controller, implemented in an FPGA. Hence, it is vital to investigate the influence of radiation on the FPGA devices. Building the transmission channel circuit based on such a device, would allow conducting this investigation simultaneously with the main task of the circuit.

#### 4.1 SRAM Based FPGA

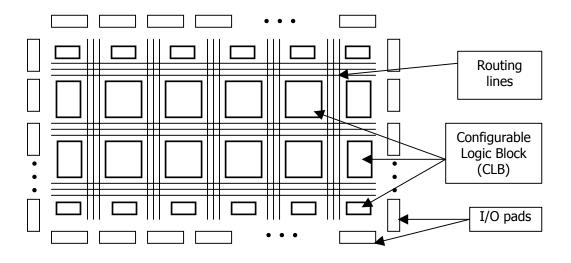

The SRAM (Static Random Access Memory) based FPGA device is the most widely used one. Numerous medical, automotive, as well as entertainment and multimedia applications are built based on the devices. The greatest market for them is, however, telecommunications [8]. SRAM-based FPGA device is re-programmable. Most of FPGA devices are constructed following a common architecture, presented in Figure 4.1.

Configuration of SRAM based FPGA is stored in SRAM, during the device's operation period. Since SRAM is volatile, the configuration is permanently stored in a non-volatile memory (ROM, EEPROM or Flash) and uploaded to the FPGA upon its start-up. Some most advanced devices are capable of being partially re-configured during full operation. The necessity of the external memory increases complexity of the PCB design. On the other hand, the use of SRAM enables the FPGA to operate at high frequencies. As described in section 3.1.2, an SRAM memory cell is highly susceptible to SEU. This poses high risk on proper device operation under neutron irradiation, as the functional configuration of the device will unpredictably change in result to such an event.

Figure 4.1. Architecture diagram of a typical FPGA device

This problem has been confirmed by an independent study [9]. The consequence of that will be circuit malfunction, a SEFI, or even device damage. To remedy the malfunction, the FPGA must be restarted, thus loading a valid configuration from non-volatile memory. This greatly degrades performance, due to delays caused by configuration uploads to FPGA or even renders the device unusable, if the Mean Time Between Functional Interrupt (MTBF) is too short for a required task to complete. The problem of detecting such changes poses additional difficulty [10], [11]. Storing the configuration in a non-volatile memory does not make it fully immune to radiation. Experiments [4] have shown, that e.g. Flash memory is erased under high TID. The device may also be damaged by a SEL. The advantage of SRAM based FPGA devices is low cost per device and unlimited number of programming cycles.

#### 4.2 Flash-based FPGA

The Flash-based FPGA device is a relatively new technology, the first devices were introduced to the market in 2002. The only company offering such devices is Actel [12]. The device is, similarly to SRAM based one, re-programmable. However, it is different from the SRAM FPGA in two respects. First, it does not require external non-volatile memory to store the configuration. This enables simpler PCB design, reduces required component count. Second, during operation of the device, the configuration is not transferred to SRAM. The Flash-based FPGA stores its configuration in (as the name implies) Flash memory. Flash is non-volatile, thus configuration is retained after power-off. What is the greatest advantage of the device is that the configuration is

used directly from Flash during device's operation. This is achieved by implementing configurable interconnections by means of flash-switches (details can be found in Actel's Flash devices datasheets [13]). The benefit of such architecture is the "live at power-up" capability of the devices – there is no time delay for configuration upload, since no upload takes place. Flash memory is also immune to soft neutron-induced effects [14], rendering the FPGA's configuration resistant to unpredictable change due to SEU. However, as mentioned in section 3.2, contents of Flash may be erased by gamma radiation, if exposed to it for extended time. The drawback of using Flash-based FPGA is lower maximum frequency, at which complicated designs can run, as compared to that of SRAM FPGA. Also the available resources are less numerous, when the most powerful devices of both families are compared. The price per available number of equivalent system gates and a limit on programming cycles the device can sustain also favours SRAM based devices.

Other FPGA devices, referred to as Flash-based, are also available on the market [15]. The Flash is embedded into the FPGA, eliminating the need of external non-volatile memory for storing configuration. However, as in SRAM based devices, the configuration is copied to that memory for the period of device's operation. This imposes the same limitations on device reliability as in case of SRAM FPGA.

#### 4.3 Antifuse FPGA

Antifuse devices use metal-to-metal connections created during programming, to define device's configuration. Hence, they are programmable only once (are not re-programmable). Because they use permanent metal-to-metal connections, they are the least volatile and least susceptible to radiation of any programmable logic technology in terms of configuration. This applies to both neutron and gamma radiation. They also are capable of operating at the highest frequencies, because the all-metal routing path is faster than one where interconnections pass through transistors. Their main drawback in the context of this project is the lack of re-programmability. When developing prototype of a device, multiple iterations of the design are unavoidable. The device, before reaching its final stage, must be verified in the field. Choosing a one-time programmable (OTP) device would require larger expenditures. Also the flexibility of the device would be compromised, as adding new components (e.g. signalling encoders or decoders) would require using a new one.

## 4.4 Radiation Hardened, Radiation Tolerant FPGA

For markets demanding level of design's reliability greater than regular (space, aerospace, defence and military), dedicated FPGA device families were developed. The effort put into the development of Radiation Hardened devices is focused on preventing SEEs from occurring. Some of these hardening methods will be briefly described in section 5.1. Radiation Tolerant devices offer lower reliability than Radiation Hardened ones. The SEEs are not prevented from occurring, but their negative effects are mitigated. This improves the reliability to a level acceptable in respective applications. Both types of devices have been in the market for less than few years. Since the technology is the newest in the FPGA sector, the most sophisticated and used in very specialized applications only, the prices of the Radiation Hardened and Radiation Hardened FPGA can range from  $\notin$ 5 000 to  $\notin$ 20 000 per one item. What is even more discouraging, available Radiation Hardened devices are one-time programmable, being based on antifuse technology. The Radiation Tolerant devices are available from different vendors in two types: SRAM based [16], and antifuse based [17].

#### 4.5 Microcontrollers

Microcontrollers can be briefly described as microprocessors fabricated with embedded program memory for storing executable code or hard-coded data (ROM, EPROM, EEPROM or Flash), Random Access Memory for volatile program data (SRAM), communication interfaces (e.g. UART, SPI, I<sup>2</sup>C) and general-purpose I/O ports (GPIO), just to mention the most common. These devices are present in virtually every electrical appliance. Their fixed hardware configuration can be, on one hand, an advantage, providing a design error-free platform for software development. On the other hand, it is a severe limitation. Supporting communication standards other than those available in embedded hardware requires either adding sophisticated external components (specialized integrated circuits) or developing software routines for that purpose. The latter solution, however, compromises overall system performance, particularly speed, and is not always feasible. The former – increases complexity of design, and introduces additional potential points of failure. The main drawback of fixed hardware architecture, in addition described, is inability to implement SEE protection mechanisms those to

other than system-level redundancy, which is firstly complicated to manage, and secondly best for manned equipment, not for autonomous [1]. The protection against SEU is particularly vital, since CPU registers in the microcontroller are implemented in SRAM. The same is true for stack, FIFO (First Input-First Output) instances of communication devices, and embedded RAM. The advantages of microcontrollers are: low price and well established development support at reasonable prices. Their generality, attained through software, is a strong pro, as well.

# 4.6 Radiation Induced Errors in Finite State Machines and Microcontrollers

The transmission channel circuit, as described in section 2.3, must be implemented as a Finite State Machine, other speaking, as a sequential system. Therefore, before commencing the design phase, possible failures arising from influence of radiation on FSMs must be identified.

Sequential systems, or FSMs, base their operation on states. States are information on the history of system's activity and its current status. In a particular instant of time, an FSM can find itself in only one particular state. Transitions between states can be either conditional or unconditional. In hardware, states are represented as data, stored in registers. In FPGA devices, registers are built using either Master-Slave D-type Flip-Flops or SRAM cells. Since both are memory elements, then, as described in section 3.1.2, are susceptible to SEU, in principle [18]. For sequential system, such an event may have disastrous consequences. Randomly negating one bit in the state register drives the FSM into unintended state. Hence, the required flow of state transitions is discontinued. The FSM may be driven either into a valid or invalid state. Being driven into the former, the system would still operate, however incorrectly. If driven into the latter, the system could enter an infinite loop or destroy volatile, but valuable data. In either case, system will encounter a malfunction.

Microcontrollers face similar problems. As mentioned in section 4.5, their working and status registers are implemented in SRAM cells. The same may apply to embedded RAM and other memory components. A SEU in any of them will falsify the data causing software to produce erroneous results, errors in communication or even collapse of the whole system. Apart from that, the hardware may behave unpredictably. Currently executed instruction, latched in Instruction Register can be changed by SEU,

making the MCU operate in a random manner. Moreover, the FSM, which manages the MCU's datapath, will fail due to SEU, as well.

To summarize, both FSMs and microcontrollers are built of components vulnerable to neutron radiation. Their behaviour will be unpredictable due to SEUs.

### 4.7 Selection of the Optimal Device

Several factors need to be taken into account, when deciding which of the, briefly presented, device families to choose for the main component of the transmission channel circuit. Since a prototype will be developed, re-programmability is very important. The specific environment, in which the final device must operate, requires the devices functional configuration to remain intact under irradiation, at least between possible servicing interventions. To meet the requirements, either a microcontroller or a Flash-based FPGA should be used. However, microcontrollers, having fixed hardware platform, cannot be protected by any SEE hardware mitigation techniques, moreover, may force the designer to use third-party components, also sensitive to radiation.

The Flash-based FPGA was chosen to house the main circuit of the transmission channel. It offers re-programmability and functional configuration unchanged under radiation (except TID effects and SEL), during devices operation, for extended periods of time. It gives flexibility on hardware level of the design, without the need to redesign from schematic and PCB. Hardware mitigation methods can be implemented and tested for effectiveness. However, the great flexibility offered by software, being the attribute of microcontrollers, is also highly demandable, as changes to e.g. communication protocol can be introduced without FPGA re-configuration. The ideal solution would be to merge the reliability and hardware flexibility of Flash FPGA with software flexibility of a microcontroller. Therefore, the decision to implement a microcontroller in the Flash-based FPGA was made. The Actel ProAsic Plus APA600 FPGA was chosen, as offering 600k equivalent system gates, yet being affordable. This, and other devices from this line, has another advantage, important in novel designs, and generally in the embedded systems market. Their FlashLock feature makes it virtually impossible to reengineer the design, disabling the possibility to copy it by competitive companies or individuals [19].

## 5 Radiation Hardening and Mitigation Techniques

This chapter is a brief summary of well known and used mitigation and hardening techniques. Section 5.1 highlights hardware hardening and mitigation against different types of SEEs. The remaining sections focus on mitigating SEUs. Most of the techniques were developed especially for high-reliability applications, such as space exploration, medical, military or satellite communications. Others come directly from telecommunications, where are used for improving transmission reliability, but can be adopted for mitigation, as well. The techniques can be characterised in two categories. Technological, realisable in hardware only, usually through modified fabrication processes of integrated circuits. Software, which can yield a system or module, which is radiation tolerant, but not hardened. This means, that the circuits operate properly up to specified levels of radiation, possibly with some loss of performance. The software techniques can be realised in either hardware or software, depending on the platform.

#### 5.1 Technological Hardening and Mitigation

The most effective, robust techniques allowing to harden electronic devices against radiation are those applied at the lowest, technology, level. They involve modified cells, being the building blocks of integrated circuits, altered structure of transistors and properly selected compounds for passivation of integrated circuits. The manufacturing technology can also decrease circuit's radiation sensitivity. The Complementary Metal Oxide Semiconductor (CMOS) technology is inherently more radiation resistant than e.g. N-type Metal Oxide Semiconductor (NMOS) one. Even greater radiation resistance is achieved in Silicon On Insulator (SOI) technology. It enables complete elimination of latch-up, due to lack of parasitic thyristor (see section 3.1.1). Additional advantages of SOI are: greater attainable frequency of operation, decreased power consumption. The drawback is the cost, as compared to standard CMOS.

Protection on higher levels of hardware has also been developed. Particular attention was paid to hardening SRAM cells, being the most frequent point of failure. One of approaches toward reducing SRAM vulnerability to ionising particles is to add series resistors on the cell's feedback paths (see Figure 3.2 for schematic of SRAM cell). The modified cell is shown in Figure 5.1.

Figure 5.1. SRAM cell with resistors in feedback paths

The benefit coming from this solution is an effective RC low-pass filter. The filter is composed of an added resistor and input capacitance of an inverter. Short transient spikes on N1 or N2 nodes can now be filtered-out by the RC network. This reduces the probability of such a spike being latched in the cell.

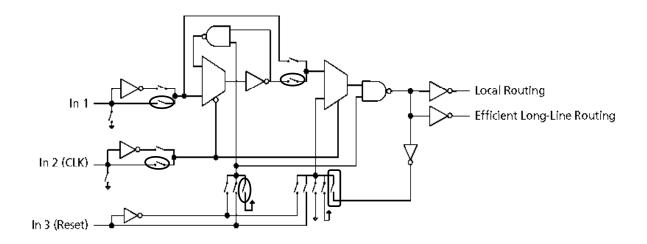

At this point it is important to mention, that the Actel ProAsic Plus devices are intrinsically hardened in a similar way. Figure 5.2 shows an elementary configurable logic cell of a ProAsic Plus FPGA [20].

Figure 5.2. Elementary configurable logic cell of Actel ProAsic Plus FPGA [20]

When the tile is configured as a storage element, a master-slave D-type flip-flop is created.

Equivalent circuit is shown in Figure 5.3.

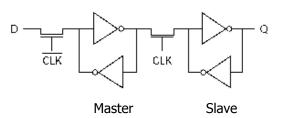

#### Figure 5.3. A Master-Slave D-type Flip-Flop

Such configuration is accomplished by closing the flash switches encircled in Figure 5.2. A flash switch is depicted in Figure 5.4

Figure 5.4. Flash switch of Actel ProAsic Plus FPGA [20]

One switch in Figure 5.2 is enclosed in a rounded rectangle. This is the only switch, which finds itself in a feedback path. This feedback constitutes to the slave latch of the flip-flop. If a voltage spike is generated by ionised particle in any of the components along the feedback path, it can potentially generate an SEU. The slave latch will be more resistant to such effects, as an RC filter is present in its feedback path. The RC network is composed of resistance of the flash switch and the input capacitance of multiplexer. The flip-flop is radiation hardened during part of the clock cycle. It is the part, during which the transistor gating the Master flip-flop is conducting. At the same time the transistor which gates the Slave flip-flop is non-conducting, i.e. the feedback path of Slave flip-flop is closed, sustaining the stored binary value.

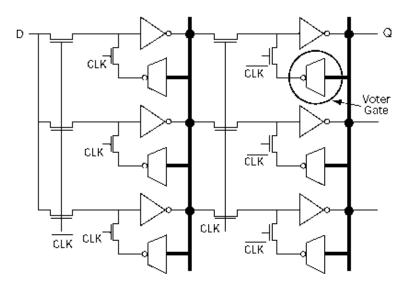

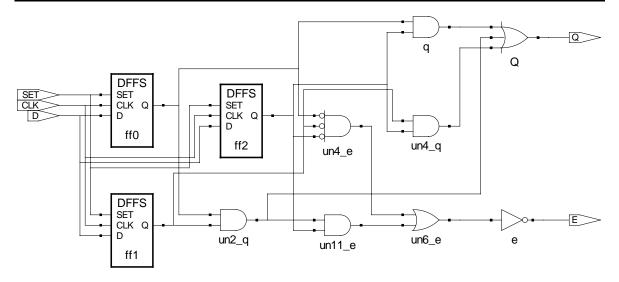

Other hardware mitigation techniques usually comprise Triple Modular Redundancy (TMR, describer in section 5.2). The TMR is applied to flip-flops or latches, with voting circuits being tripled, as well. An example of flip-flop tripled on the latch and voter level is shown in Figure 5.5.

Figure 5.5. D-type Flip-Flop hardened with TMR [21]

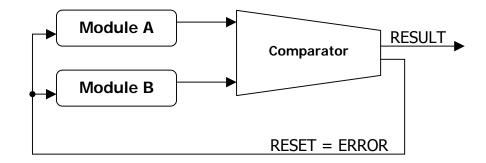

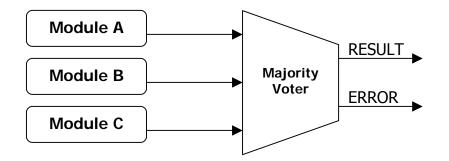

#### 5.2 Double Modular Redundancy, Triple Modular Redundancy

The technique of modular redundancy is most widely used in high-reliability applications. There are various kinds of this scheme, depending on the number of single module replications. Thus, there is Double (DMR) and Triple (TMR) Modular Redundancy – the most common, there may also be Quintuple Modular Redundancy (QMR) or other of higher order (xMR). This scheme is used from car or aircraft control and safety systems, power plant systems to military and space ones. Either the whole system or subsystem can be replicated or only its most vulnerable modules. There may be two types of modular redundancy. First when only one system or module is operating at given time. The module or system is diagnosed. Once it undergoes malfunction it is disconnected and the back-up system or module takes over its function. The additional entity is referred to as *cold reserve*. The second is based on voting. In DMR two entities function in parallel, performing the critical tasks in the same instants of time. The scheme is also referred to as *hot reserve*. The outcomes of the task, coming from the two entities are fed to a voter, or simply a comparator (see Figure 5.6). Whenever the results are different an error is signalled. The redundant system has entered an erroneous state.

It cannot recover from it, as there is sufficient information only to detect the error, no correction is possible. The two modules or systems produced different results, but it is unknown which one is correct. Therefore, the systems must be restarted, in order to initialise them with known and correct values.

#### Figure 5.6. The idea of DMR

TMR is more capable. In this scheme every critical entity is tripled. A voter, more sophisticated than the comparator in DMR scheme, is fed with outputs from every entity. The voter decides on the result, by performing majority voting (see Figure 5.7). The result is as indicated by at least two entities. If the representation of outputs from the entities is binary, the voter is always able to decide, it is never confused. Hence, the TMR scheme is not only capable of detecting an error, but also correcting it. For the reason, it is able to sustain system's operation if an error is encountered. This capability can pose a potential threat. If two or all three modules are corrupted by error, the TMR will not notice it, and proceed as if the error was not present or was corrected. The limitation of TMR is that it can correct single errors only.

#### Figure 5.7. The idea of TMR

Many times a designer faces a dilemma, which xMR technique to choose. Both DMR and TMR are capable of detecting system's malfunction. The DMR requires a restart

in such a situation, thus destabilising the system and compromising performance. The TMR scheme allows for continuous operation, at higher cost, however. TMR requires more resources than DMR and a more sophisticated voter. The tripled entities must be well synchronised not to generate some transient states at the voter output. For applications, which do not require continuous operation the DMR scheme is an optimal choice. The TMR should be applied in critical high-reliability designs.

In every xMR scheme the voting circuit becomes the vulnerable element, as not being replicated. Measures must be taken to minimise its sensitivity to radiation.

#### 5.3 Hamming Codes

Hamming codes belong to the family of Forward Error Correcting (FEC) codes. They stem from digital communications, where are used for increasing communication reliability. They are also used in ECC computer memories. Hamming Codes rely on adding redundant bits to the transmitted word of information. The redundancy is used at the receiver to detect and correct errors. Hamming Codes are capable of detecting and correcting all single-bit errors within a word. Detection of double errors is also possible, but the amount of redundant information is insufficient to correct such errors. The theory behind Hamming Codes is based on matrix multiplication in finite field (Galois Field) arithmetic [22]. The Hamming rule ensures that all single-bit errors are correctable - the distance between two codewords is equal to 3, i.e. any two codewords of a particular Hamming Code differ in at least three positions, in binary. Hamming Code can be constructed for any  $m \ge 2$ , where m is the number of check bits. The Hamming rule is given by:

$$n = 2^m - 1$$

$$k = 2^m - m - 1$$

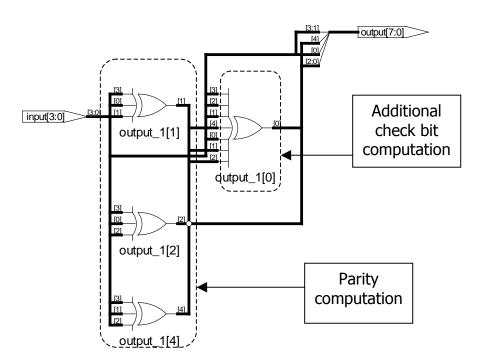

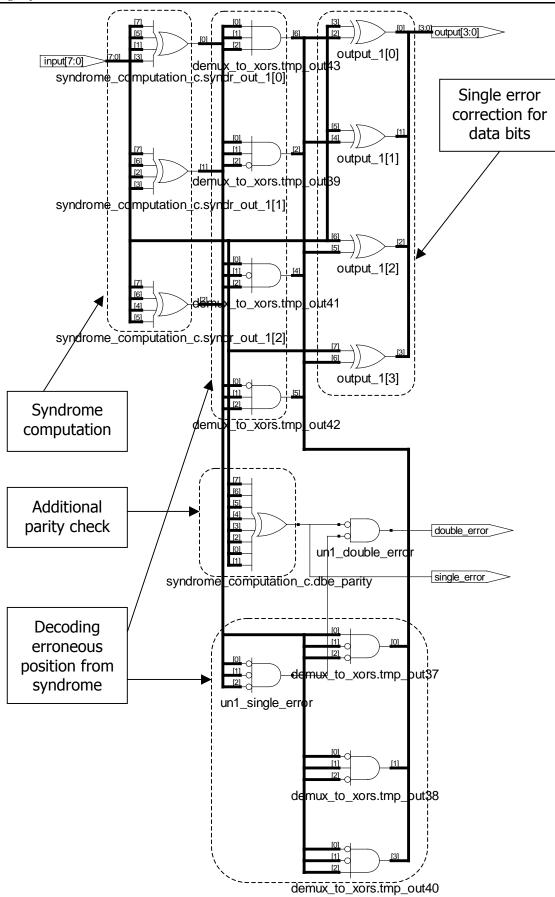

The k is the length of the data vector, n designates the length of codeword and m is the number of check bits. Code with such parameters is a *perfect code*. For the code to have the double error detecting capability, additional check bit is required, thus the double error detecting, single error correcting Hamming Code has m+1 check bits. Its length n is  $2^m$ . Generally, such code is designated (n, k) Hamming Code. From the engineer's point of view the conclusions following from the matrix operations are most valuable, as they provide him with a straightforward method to implement Hamming Codes without the need of matrix operations. This is explained on an example of (8, 4) double error detecting, single error correcting Hamming Code.

The parity check bits are located at positions *p*, which fulfil the condition:

$$2^i = p,$$

for non-negative integer *i*, such that p < n. Therefore, for the exemplary code the check bits are placed at positions: 1, 2 and 4. The additional check bit for double error detection is placed at position 0. The check bits are even-parity bits for groups of data bits. The data bits, starting from the least significant, are assigned the remaining positions within the codeword, starting from the lowest position available. The resultant codeword is shown in Figure 5.8.

| Bit 7 | Bit 6 | Bit 5 | Bit 4     | Bit 3 | Bit 2 | Bit 1 | Bit O |

|-------|-------|-------|-----------|-------|-------|-------|-------|

| D3    | D2    | D1    | <i>C3</i> | D0    | С2    | C1    | CO    |

Figure 5.8. Structure of (8,4) Hamming Code codeword. 'D' – data bit, 'C' – check bit

The binary representation of check bit's position (cb) determines the bits for which it is computed. The binary value is used as a mask. Every position (bp), except position 0, is masked with the value. If the result of masking is the check bit position (cb), then the bit at position (bp) contributes to the computation of check bit. For the (8, 4) code one obtains groups of bits shown in Table 5.1. The additional check bit at position 0 is a parity check over all codeword's bits.

| Check bit position | Bits in the group   |

|--------------------|---------------------|

| 1                  | 3, 5, 6             |

| 2                  | 3, 5, 7             |

| 4                  | 5, 6, 7             |

| 0                  | 1, 2, 3, 4, 5, 6, 7 |

Table 5.1. Contribution of codeword's bits to parity checks

When the codeword is received, the data bits along with check bits are used to compute a *syndrome*. The additional check bit is not employed in the computation of syndrome. It is used along with all the other bits to make additional parity check. The syndrome computation is parity check for all the bit groups, except 0<sup>th</sup> bit group. The syndrome is composed of computed parity values.

The position of a value in the syndrome is given by:

$S_{position} = \log_2(group's \ check \ bit \ position \ in \ the \ codeword)$

If the value of syndrome is zero and parity check for the additional bit passes, the codeword was received correctly. If the syndrome is zero, but additional parity check fails, the additional parity bit is corrupted by error. It is a single error, correctable by the code. In another case, when syndrome is non-zero and additional parity check fails, the additional bit is correct, but one of the others is corrupted. Again, a correctable single error has been encountered. In the last case, when syndrome is non-zero and additional check passes, the received codeword has a double error. The value of syndrome in case of a single error indicates the erroneous position. In this way not only the data bits can be recovered, but also the check bits.

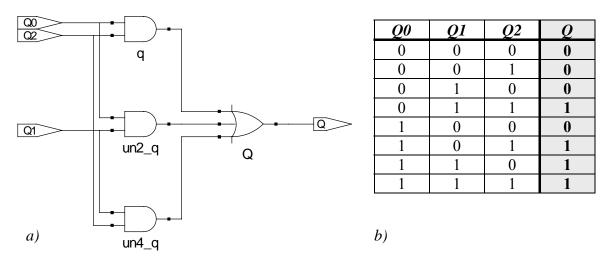

The described interpretation was used throughout this project to implement purely combinatorial Hamming Code encoders and decoders. Examples are shown in Figure 5.9 and Figure 5.10.

Hamming Codes are suitable for protecting both, memory arrays and distributed registers.

Figure 5.9. Purely combinatorial encoder for (8,4) Hamming Code

Figure 5.10. Purely combinatorial decoder for (8,4) Hamming Code

### 5.4 2-D parity Checking

The 2-D (two-dimensional) parity is a technique used for protecting memories or their blocks. In contrast to Hamming Codes, this method is not suitable for mitigating single words of data. The idea of 2-D parity is explained in Figure 5.11. The memory is first subdivided into blocks of known size. The size should be adjusted according to expected rate of SEUs and memory read attempts. Every block contains an even number of words. Such a cluster may be treated as a binary matrix, with words being its rows, while vectors of bits of the same significance, the columns of the matrix. For every row and column a parity bit is assigned. The even-parity scheme is used, i.e. the number of '1s' of a row or column along with the parity bit is always even. The value of the parity bit is chosen to satisfy the condition, parity generation. The even-parity can detect any odd number of errors, but is unable to detect a double error. The simple parity is also unable to correct any error, since there is no information available on its location. This is not a limitation of the 2-dimensional parity. It is capable of correcting all single-bit errors within the protected block. The method is also capable of detecting a double-bit error within either a row or a column, but its correction is not possible. The drawback of 2-D parity, as compared to Hamming Codes, is the inability to read the word of data and correct it on the fly, since the parity bits must also be read. Since at least three read cycles are necessary, read data has to be temporarily stored, resulting in jeopardizing it due to SEU.

| Bit<br>Address   | 3 | 2 | 1 | 0 | Row<br>parity |

|------------------|---|---|---|---|---------------|

| 0x00             | 1 | 0 | 0 | 1 | 0             |

| 0x01             | 1 | 1 | 1 | 0 | 1             |

| 0x10             | 0 | 0 | 1 | 0 | 1             |

| 0x11             | 0 | 1 | 0 | 1 | 0             |

| Column<br>parity | 0 | 0 | 0 | 0 |               |

| Bit<br>Address                          | 3 | 2 | 1        | 0 | Row<br>parity         |  |

|-----------------------------------------|---|---|----------|---|-----------------------|--|

| 0x00                                    | 1 | 0 | 0        | 1 | 0                     |  |

| 0x01                                    | 1 | 1 | 1        | 0 | 1                     |  |

| 0x10                                    | 0 | 0 | <u>0</u> | 0 | <b>▲</b> <sup>1</sup> |  |

| 0x11                                    | 0 | 1 | 0        | 1 | 0                     |  |

| Column<br>parity                        | 0 | 0 | 0        | 0 |                       |  |

| Incorrect parity<br>values due to error |   |   |          |   |                       |  |

Single error within 4x4 block

Figure 5.11. 2-D parity and single-error correction example

## 5.5 Scrubbing

Scrubbing cannot be used as a standalone technique of mitigation. It has no inherent error detection or correction capabilities. This technique requires redundancy of data capable of correcting errors e.g. TMR, Hamming Codes or 2-D parity. Other techniques, which enable error detection or correction, are well suited, too. The general idea behind scrubbing is refreshing. It is executed periodically. The memory, its block or other data storage entity is sequentially read, word by word. The employed mitigation technique is used to assess whether data within read word is correct or not. In the latter case, the error correction follows, according to the mitigation technique. The corrected data is written back and the process continues, until whole storage space has been swept. Scrubbing is an important technique, as it prevents errors from accumulating. By carefully choosing and adjusting mitigation technique and the rate at which scrubbing is executed, one can minimise the risk of encountering a non-correctable error. In this way system stability is sustained for extended periods of time. There are drawbacks of scrubbing, too. The resource, which is being refreshed, cannot be accessed by the system. This requires the system to be halted if it claims the refreshed resource. Another solution could be executing scrubbing partially, for resources not being currently used. This, however, is not possible e.g. for memory storing program code. Therefore, the system will suffer some loss of performance if scrubbing is employed. It is important to state, that scrubbing itself is vulnerable to radiation, since an FSM handles it and should be mitigated.

# 6 Project Description

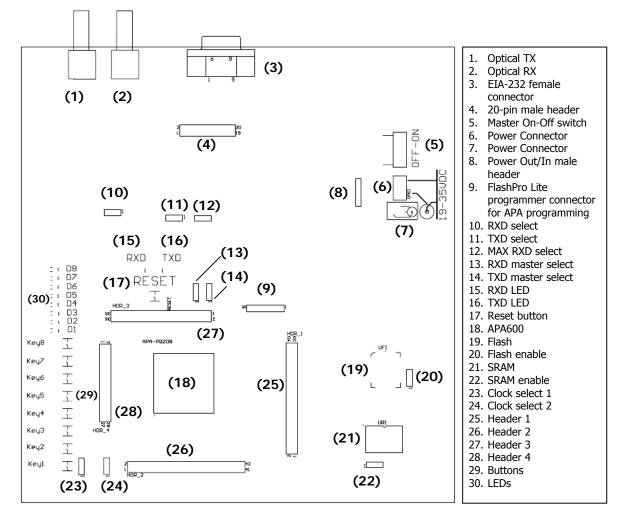

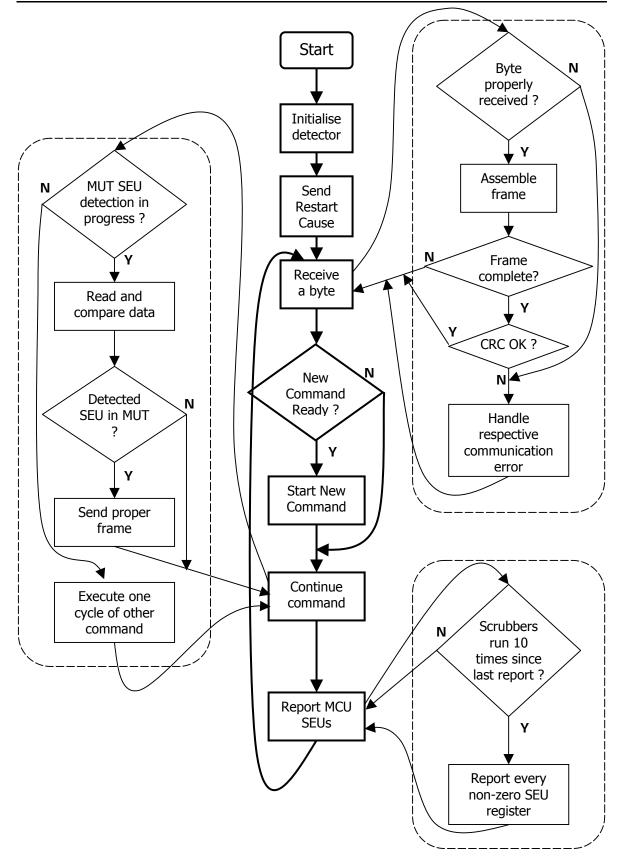

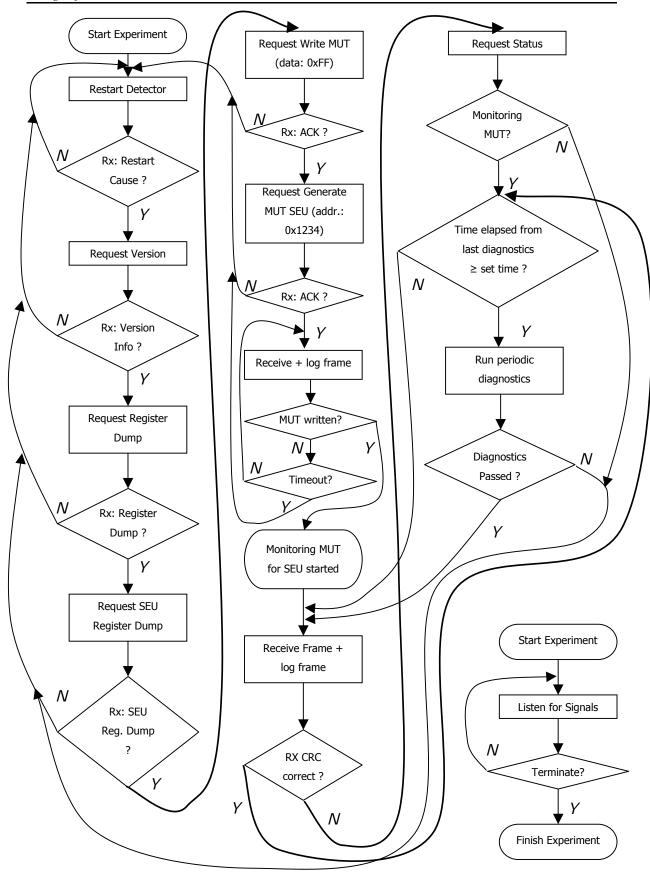

This chapter gives a description of the implemented transmission channel circuit. The overall structure of the circuit is presented, followed by a more detailed description. The techniques, which were employed to improve circuit's radiation tolerance are further described and assisted with relevant examples of code. Next, the designed hardware platform is presented. Finally, the software for an exemplary application, namely SRAM SEU detector, is described.

#### 6.1 Overview

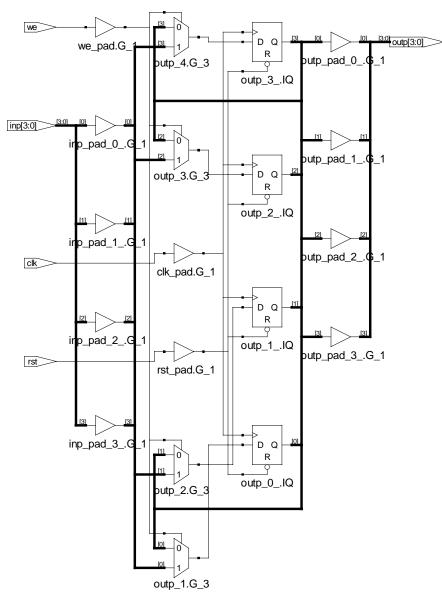

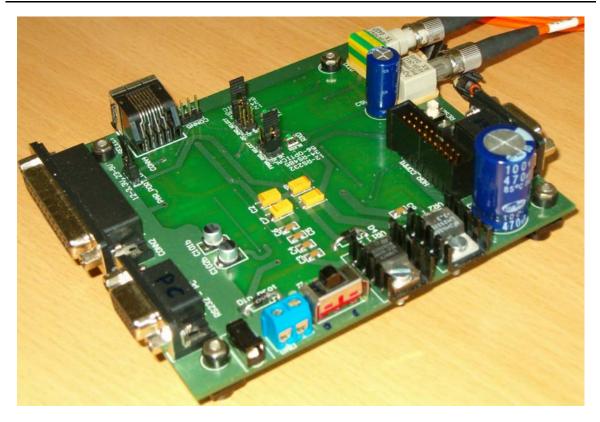

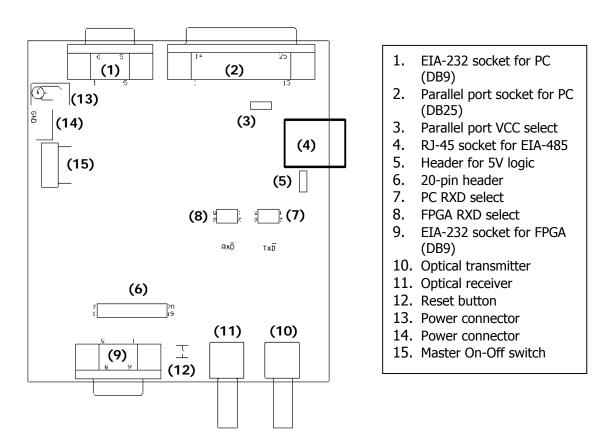

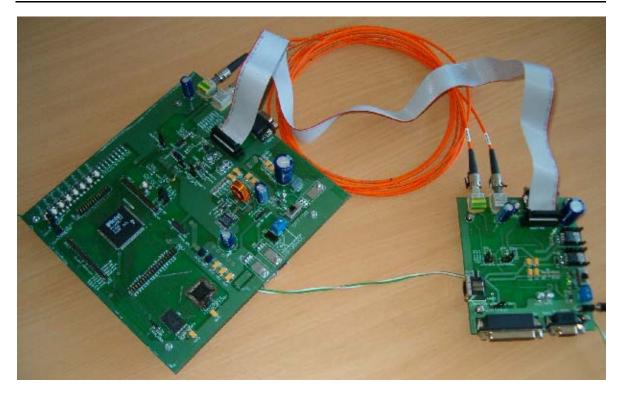

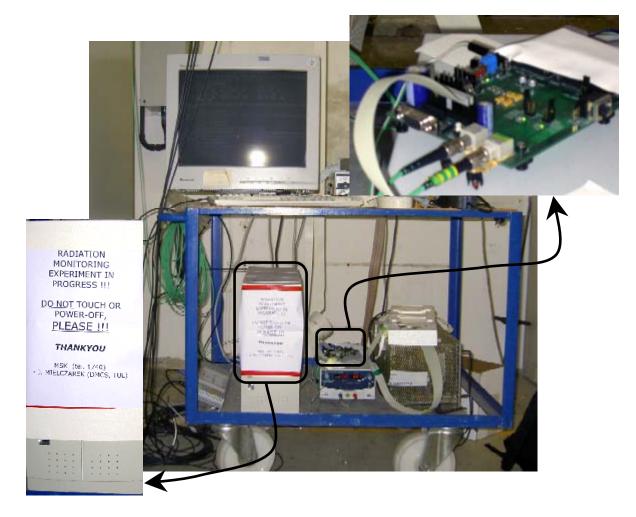

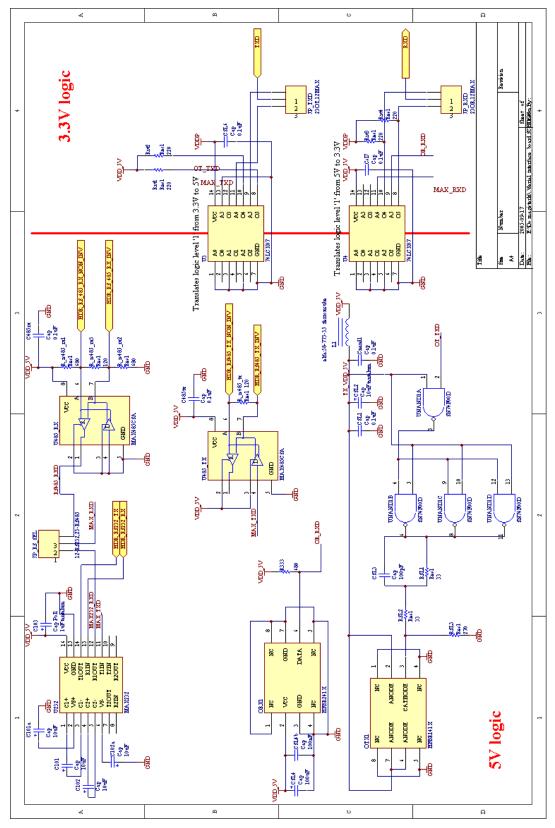

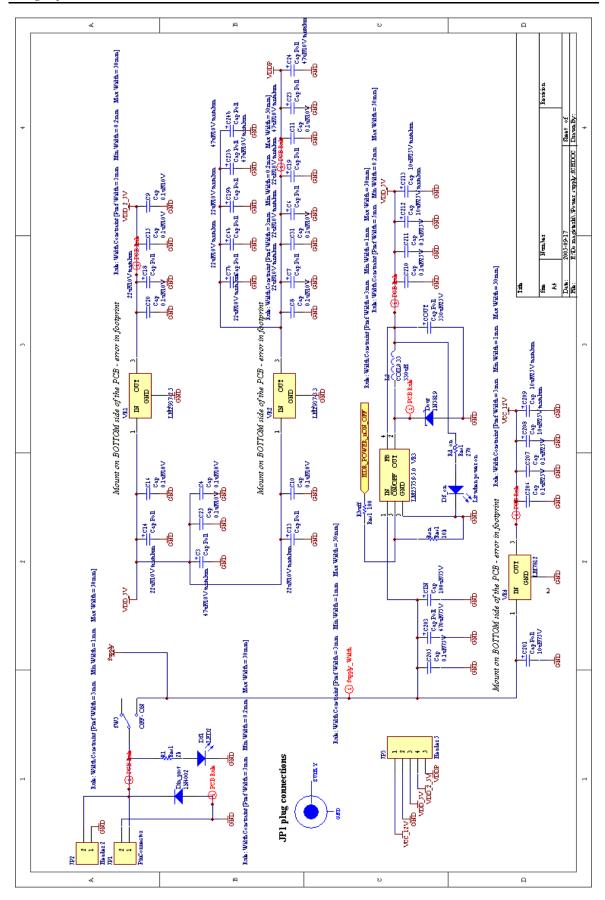

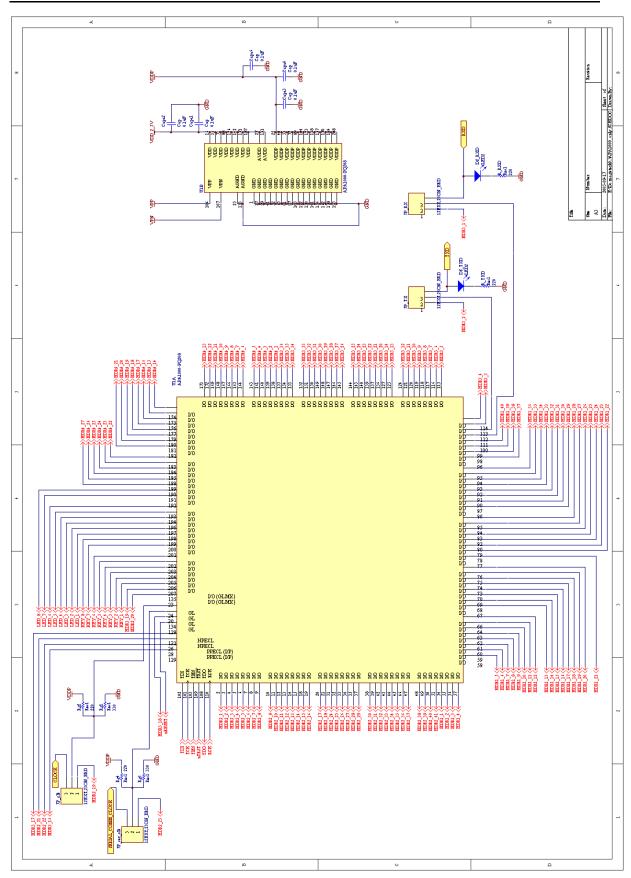

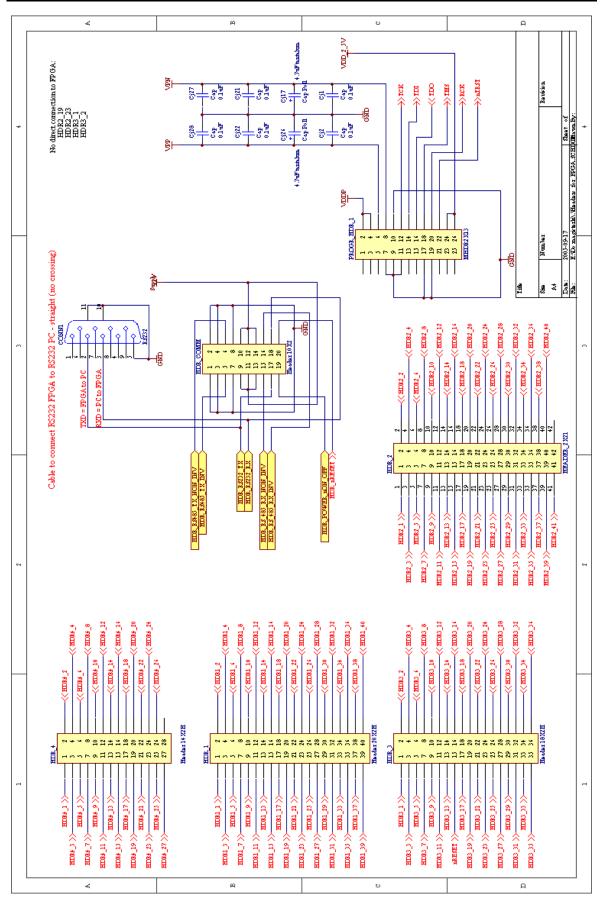

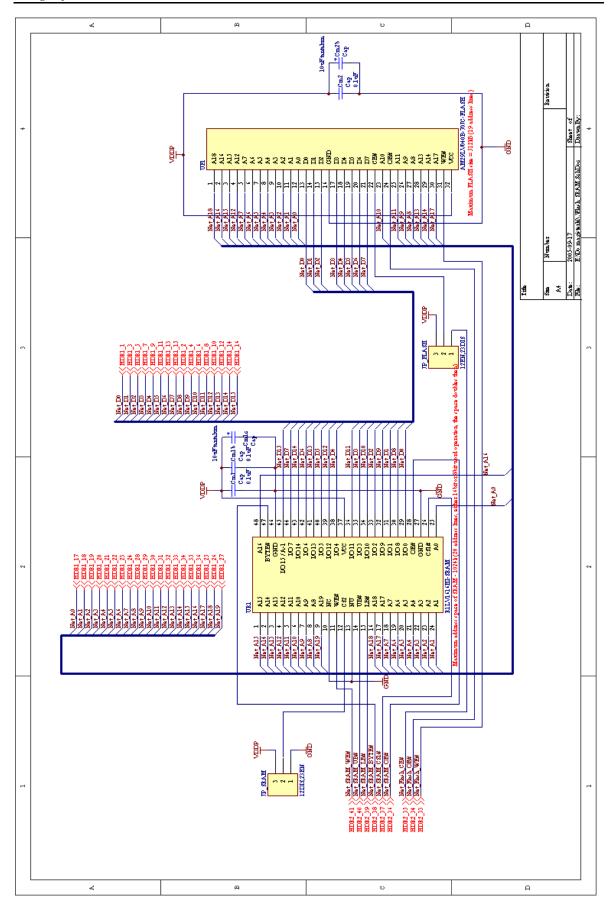

The transmission channel circuit was implemented in FPGA. As it was mentioned in section 4.7, to achieve high flexibility, the circuit relies on a microcontroller core. The microcontroller chosen is Microchip's [23] PIC16C57 [24]. The Microcontroller Unit (MCU) was significantly augmented, the details are described in section 6.2. In order to demonstrate the functionality of the circuit, a complete communication channel was built, with the MCU at one end, and a PC at the other. The PC functions as a monitoring and command station. The medium chosen for transmission of signals is a full-duplex optical fibre, however other media are also supported. In order to interface the optical signals to the PC and meet requirements described in section 2.2, the transceiver was built, as well. The diagram shown on Figure 6.1 depicts the structure of the complete communication channel. The PC communicates with the MCU via serial port, in conformance to EIA-232 protocol. The serial communication signals can be further carried, apart from optical link, over differential EIA-485 or again EIA-232. On the MCU side an UART is responsible for serial transmission. The EIA-232 and EIA-485 signals are carried over 20-wire ribbon cable, together with RESET and POWER-OFF signals and power supply. To support MCU's re-programmability, external Flash and SRAM modules are installed. The MCU communicates with external devices, such as DUT (Device Under Test) by means of GPIO (General-Purpose Input/Output) ports.

Figure 6.1. Detailed block diagram of the communication channel set-up

# 6.2 Radiation Tolerant MCU Based on PIC16C57

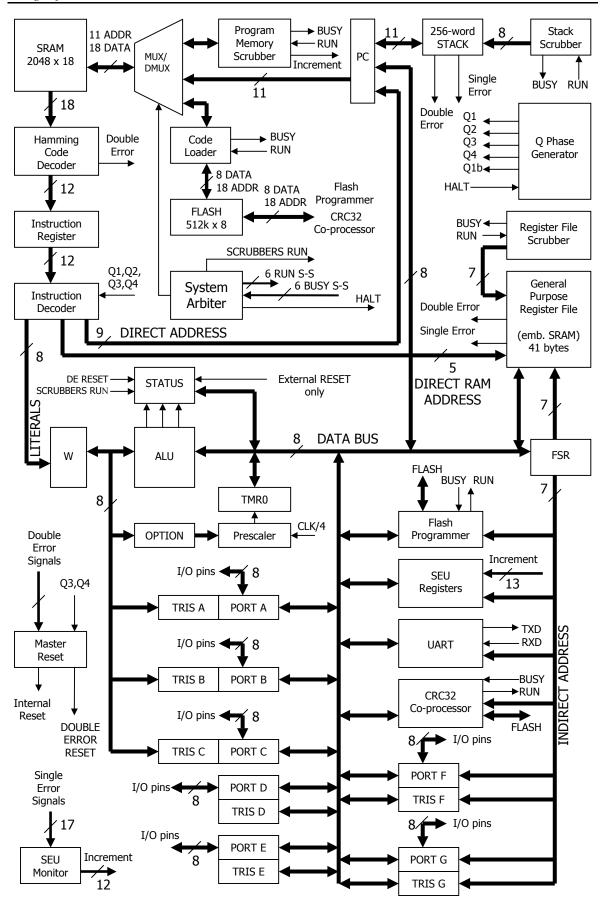

The transmission channel circuit is based on the PIC16C57 microcontroller [24]. The MCU is designed in the Harvard architecture, what speeds-up program execution and enables pipelining. The MCU core is of RISC (Reduced Instruction Set Computer) type. There are only 33 instructions [24], most of them need one machine cycle to execute. The CALL and GOTO instructions take two cycles to execute. The MCU has 2048-word program memory and 128-byte register file, arranged in 4 banks (0 - 3). Due to mapping of some registers into bank 0 and the fact that some Special Function Registers and peripheral devices are mapped into the register file address space, the effective size of register file is 72 bytes. This MCU has been implemented in the Actel ProAsic Plus APA600 FPGA. The functional block diagram is presented in Figure 6.2. The great advantage of having a flexible hardware platform, compliant with a widely supported standard, is the ability to develop software for it, and what is more, be capable of augmenting or changing peripheral hardware without the need to redesign the PCB. The tools for software development, such as C or Basic compilers for the MCU, are already present and constantly improved. The basis for developing the MCU was description of PIC16C5 core written in VHDL. The core is published under GPL (General Public License) on [26]. The basis core is significantly limited according to PIC16C57 specification. It is also impaired by several errors. Therefore, corrections were necessary, before the core could be used for the transmission channel circuit. The original code was written in VHDL (Very High Speed Integrated Circuit Hardware Description Language), so this HDL (Hardware Description Language) was used for the description of all required hardware, implemented in the FPGA. The following functional features of the PIC16C57 were either not present, and were added, or needed to be corrected:

- generator of MCU phases and properly operating 2-stage pipeline,

- four banks of registers in the register file,

- mapping registers with addresses 0x0 0xF from each bank to registers 0x0 0xF in bank 0,

- support for 2048-word program memory,

- assignment of status bits to their proper functions,

- addition and subtraction in ALU (Arithmetic Logic Unit),

- Timer, Prescaler and Option register.

Figure 6.2. Functional block diagram of Radiation Tolerant MCU based on PIC16C57

The internal watchdog was not embedded due to existence of monitoring station, which also performs the function of an external watchdog.

To further extend the functionality of the circuit, several additional components were added. The main features of the modified MCU are summarised in Table 6.1.

| Component                                     | Purpose                                                                                                                                                                                                                |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 GPIO ports, 8 independent I/Os each         | Enables convenient communication with DUT                                                                                                                                                                              |

| 256-word deep stack,<br>extended from 2 words | Improves reuse of code, effectively decreasing its size                                                                                                                                                                |

| CRC32 co-processor                            | Computes and verifies CRC32 for blocks of<br>data, significantly decreasing size of code<br>required for accomplishing this task;<br>speeds-up program execution by taking-off<br>computational load from the MCU core |

| UART                                          | Handles serial communication compliant<br>with EIA-232 protocol; takes-off<br>communication handling from the MCU<br>core, speeding-up program execution and<br>reducing code size                                     |

| Code Loader                                   | After Reset or Power-On copies code from<br>Flash to SRAM for faster code execution                                                                                                                                    |

| Flash programmer                              | Handles Flash programming; extends<br>programmability of PIC16C57<br>(the Microchip's device is OTP)<br>to re-programmability                                                                                          |

| System Arbiter                                | Manages the MCU core and all embedded<br>components, which require access<br>to external memory                                                                                                                        |

Table 6.1. Summary of components of the modified MCU based on PIC16C57

The most important requirement for the transmission channel circuit is improved radiation tolerance. For that reason the MCU is backed by specialised components. Moreover, to enable observability of SEUs in the MCU a monitor was also embedded. The components are summarised in Table 6.2.

| Component               | Purpose                                                                                                                                           |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Program Memory Scrubber | Scrubs the Program Memory. If during<br>scrubbing a single error in the memory is<br>encountered, the appropriate SEU register is<br>incremented. |

| Register File Scrubber  | Scrubs register file                                                                                                                              |

| Stack Scrubber          | Scrubs stack                                                                                                                                      |

| SEU Monitor             | Monitors groups of components for<br>occurrence of SEU. Once a SEU is spotted,<br>the appropriate SEU register is incremented.                    |

| SEU registers           | Store the number of SEUs detected in the MCU. Content of such register is automatically cleared by hardware after reading.                        |

| Master Reset            | Monitors for occurrence of double error in<br>any of the SRAM components, resets<br>the MCU if such error is spotted                              |

| Table 6.2. Summary of components necessary for improved radiation tolerance and |

|---------------------------------------------------------------------------------|

| diagnosis of the MCU                                                            |

Most relevant components are further described. Details on scrubbers and Master Reset can be found in section 6.2.2.1. The map of register file is collected in Table 6.4.

The Status register bits have in some cases different function than in the Microchip's PIC16C5. These differences have no impact on compatibility with existing tools for the MCU. The Status register bits, which have different function than original are described in Table 6.3.

| Bit | Function                                                                                                                                                                                                                                                                                                                                         | Original function |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 3   | Scrubbers Run flag.Power down. Used in<br>conjunction with SLEEP<br>instruction, which is not<br>implemented.                                                                                                                                                                                                                                    |                   |

| 7   | Enables software to check if scrubbers were run.implemented.Double Error Reset flag.<br>Set by hardware prior to performing soft reset caused<br>by double error in SRAM components.byCleared by software.<br>Enables software to determine the cause of last<br>restart:<br>'1' - double error caused<br>'0' - power-on or normal resetNot used |                   |

Table 6.3. Modified Status Register bits

| Address | Register name    | Component             | Description                                                              |

|---------|------------------|-----------------------|--------------------------------------------------------------------------|

| 0x00    | Indirect         |                       |                                                                          |

| 0x01    | TMR0             |                       |                                                                          |

| 0x02    | PCL              |                       |                                                                          |

| 0x03    | STATUS           |                       | [24]                                                                     |

| 0x04    | FSR              | None                  | [24]                                                                     |

| 0x05    | PORTA            |                       |                                                                          |

| 0x06    | PORTB            |                       |                                                                          |

| 0x07    | PORTC            |                       |                                                                          |

| 0x51    | SEU_RS_SS        |                       | SEU detected in Program Memory Scrubber<br>or Stack Scrubber             |

| 0x52    | SEU_A_RS_CL      | SEU register          | SEU detected in System Arbiter, Register<br>File Scrubber or Code Loader |

| 0x53    | SEU_CRC32        |                       | SEU detected in CRC32 co-processor                                       |

| 0x54    | CRC32_GEN        | CRC32<br>co-processor | Input/Output register                                                    |

| 0x55    | FP_CMD_STAT      | -                     |                                                                          |

| 0x56    | FP BLS L         | ]                     |                                                                          |

| 0x57    | FP BLS M         | T11                   |                                                                          |

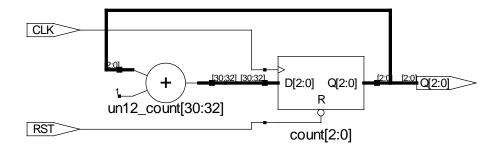

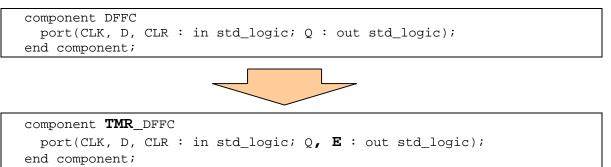

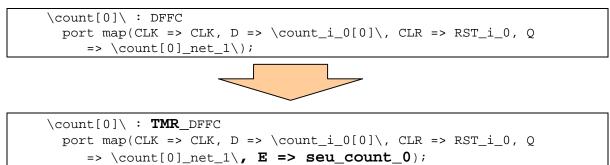

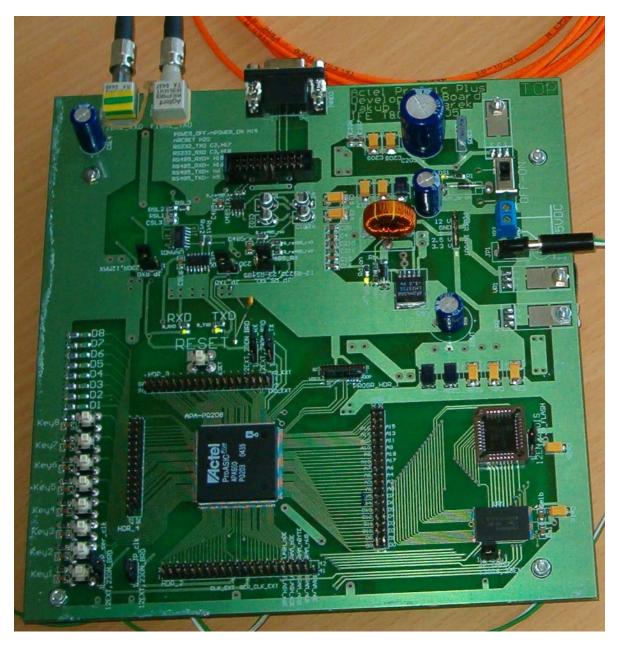

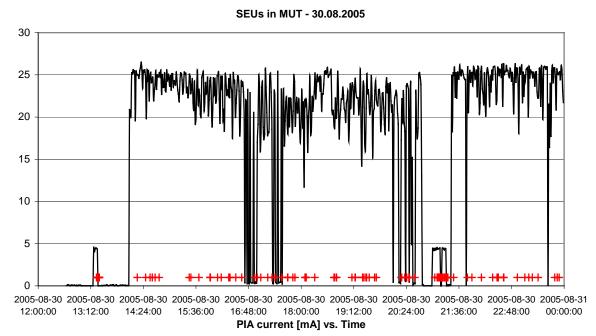

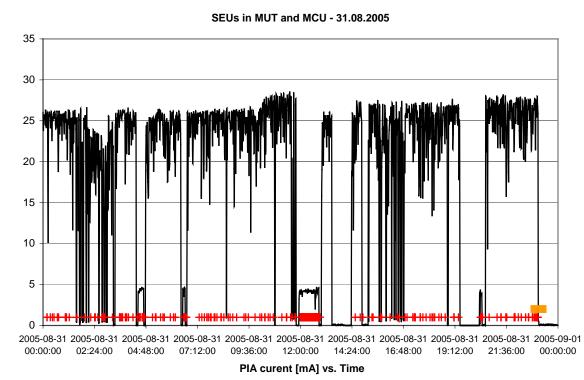

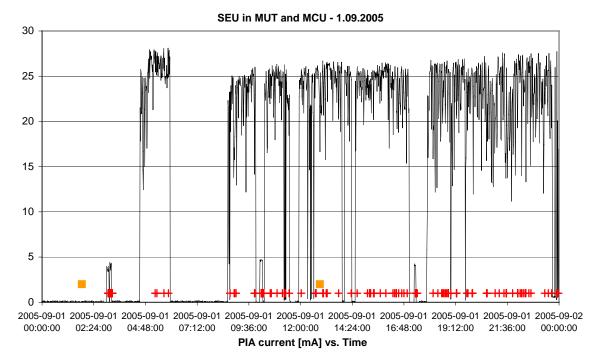

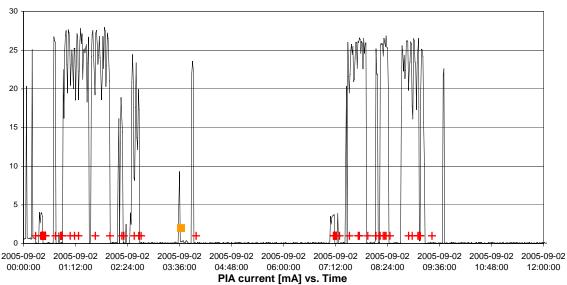

| 0x58    | FP BLS H         | Flash                 | Table 6.10                                                               |