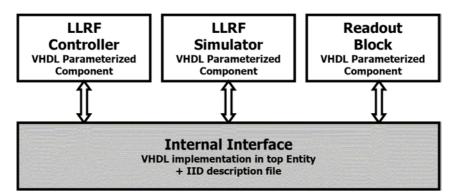

Internal Interface

## I/O communication with FPGA circuits and hardware description standard for applications in HEP and FEL electronics ver. 1.0

## Krzysztof T. Pozniak

Institute of Electronic Systems, Warsaw University of Technology, ELHEP Laboratory Nowowiejska 15/19, 00-665 Warsaw, Poland www.desy.de/~elhep, pozniak@ise.pw.edu.pl, tel.+48-22-660-79-86 fax.+48-22-825-23-00

## ABSTRACT

The work describes hardware layer of the universal, parameterized communication interface for application in the FPGA chips. The interface is called in this work as the *"Internal Interface*" or in short the "*II*". The paper shows how to automatically create the address and data space, according to the user declarations. The methods to standardize the I/O communication with FPGA chips are described. The communication uses library functions and standardized, parametric components in VHDL. Theoretical background and technical description of the *Internal Interface* are illustrated with a few easy examples of simple interfaces.

The name of *"Internal Interface*" is used by the author and the Warsaw ELHEP Research Group since 2000 for the description of then newly introduced I/O communication standard between the user and the FPGA chip. The *Internal Interface* communication standard has been applied since its first introduction in:

- Muon and Energy Trigger for Backing Calorimeter (BAC) in ZEUS experiment (AHDL version) [11],

- RPC Muon Trajectory Pattern Comparator Electronics for Compact Muon Solenoid (CMS) in CERN [15],

- TESLA Low Level RF Control electronics for TTF II and VUV FEL, as well as for X-Ray FEL studies [17-22],

- Warsaw ELHEP Laboratory on Electronics for High Energy Physics Experiments for teaching purposes and FPGA electronics development [10] in WUT,

- WARSAW CMS Laboratory, for CMS electronics development [14] in the Institute of Experimental Physics, WU,

**Keywords**: FPGA, FPGA I/O, VHDL, Altera, Xilinx, communication interface, behavioral programming, FPGA systems parameterization and standardization, FPGA based systems for HEP experiments, multi-FPGA systems.

## Contents

| 1 | INT  | RODUCTION                                                       | 4  |

|---|------|-----------------------------------------------------------------|----|

| 2 | PAI  | RAMETRIC HARDWARE BUS                                           | 6  |

| 3 | DE   | CLARATION OF RECORD LIST FOR INTERFACE                          | 8  |

|   | 3.1  | Record type – ItemType                                          |    |

|   | 3.2  | RECORD IDENTIFIER – ITEMID                                      |    |

|   | 3.3  | SCALING PARAMETERS – ITEMWIDTH, ITEMNUMBER                      |    |

|   | 3.4  | RECORDS GROUPING – ITEMPARENTID                                 |    |

|   | 3.5  | ACCESS RIGHTS TO RECORD – ITEMWRTYPE, ITEMRDTYPE                |    |

|   | 3.6  | RECORD DESCRIPTION – ITEMNAME, ITEMFUN, ITEMDESCR               | 11 |

| 4 | TH   | E BASICS OF INTERFACE IMPLEMENTATION                            | 12 |

|   | 4.1  | PHYSICAL PARAMETERS OF INTERFACE - II_ADDR_WIDTH, II_DATA_WIDTH | 12 |

|   | 4.2  | SPLITTING OF ADDRESS AREA FOR PHYSICAL RECORDS                  |    |

|   |      | 4.2.1 Partitioning of VII_WORD                                  | 12 |

|   |      | 4.2.2 Partition of VII_BITS for vector VII_VECT                 |    |

|   |      | 4.2.3 Partition of VII_AREA                                     |    |

|   | 4.3  | PAGING OF THE ADDRESS AREA - VII_PAGE                           |    |

|   | 4.4  | INTERFACE IMPLEMENTATION TABLE                                  |    |

|   |      | 4.4.1 Address parameters – ItemAddrPos, ItemAddrLen             |    |

|   |      | 4.4.2 Interface vector parameters – ItemWrPos, ItemRdPos        |    |

|   |      | 4.4.3 Record of parameters initializing the interface           | 17 |

| 5 | INT  | <b>ERFACE IMPLEMENTATION</b>                                    | 18 |

|   | 5.1  | LIBRARY FUNCTIONS                                               | 18 |

|   | 5.2  | STANDARD INITIALIZATION OF INTERFACE                            |    |

|   | 5.3  | STANDARD SERVICE OF INTERFACE                                   | 19 |

|   | 5.4  | USER FUNCTIONS                                                  | 22 |

| 6 | EX   | AMPLE OF INTERFACE IMPLEMENTATION                               | 26 |

|   | 6.1  | PROJECT OF RECORDS FOR INTERFACE DECLARATION LIST               | 26 |

|   | 6.2  | CALCULATION OF INTERFACE IMPLEMENTATION TABLE                   |    |

|   | 6.3  | EXEMPLARY SOURCE CODE FOR INTERFACE IMPLEMENTATION              | 28 |

|   | 6.4  | FUNCTIONAL SIMULATION OF SIGNAL TIME RELATIONS IN INTERFACE     |    |

|   | IMPI | LEMENTATION                                                     | 30 |

| 7 |      | PLEMENTATION OF PARAMETRIC, EXTERNAL, FUNCTIONAL                |    |

|   | CO   | MPONENTS                                                        |    |

|   | 7.1  | IMPLEMENTATION OF EXTERNAL REGISTER FOR READ BUFFERING          |    |

|   | 7.2  | IMPLEMENTATION OF EXTERNAL PARAMETRIC COUNTER                   |    |

|   | 7.3  | IMPLEMENTATION OF PARAMETRIC EXTERNAL MEMORY                    | 38 |

| 8  | CONCLUSIONS AND CLOSING REMARKS                                                                                                  | 41       |

|----|----------------------------------------------------------------------------------------------------------------------------------|----------|

| 9  | REFERENCES                                                                                                                       | 45       |

| 10 | ACKNOWLEDGMENTS                                                                                                                  | 47       |

| AP | PPENDICES                                                                                                                        | 48       |

| A  | VHDL LIBRARY FILES                                                                                                               | 48       |

|    | A.I FILE "STD_LOGIC_1164VHD"<br>A.II FILE "VCOMPONENT.VHD"                                                                       | 48<br>49 |

| B  | APPLICATIONS OF INTERNAL INTERFACE FOR HEP EXPERIMENT<br>AND ACCELERATOR LLRF CONTROL                                            |          |

| С  | PROGRAMMING LAYER OF INTERNAL INTERFACE                                                                                          | 53       |

|    | C.I INTERNAL INTERFACE CONTROL SYSTEM IN C++                                                                                     |          |

|    | C.II INTERNAL INTERFACE CONTROL VIA C++ AND MATLAB                                                                               |          |

|    | C.III INTEGRATION OF INTERNAL INTERFACE WITH DOOCS AND MATLAB<br>C.IV INTEGRATION OF INTERNAL INTERFACE WITH XDAQ SYSTEM FOR CMS |          |

| D  | DEVELOPMENT OF INTERNAL INTERFACE                                                                                                | 58       |

| E  | EXAMPLES OF COMMERCIAL COMMUNICATION STANDARDS                                                                                   | 59       |

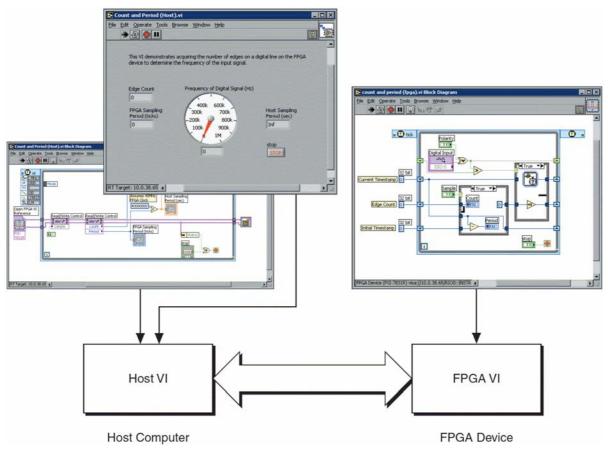

|    | E.I INTEGRATION OF LAB VIEW WITH FPGA MODULES                                                                                    | 59       |

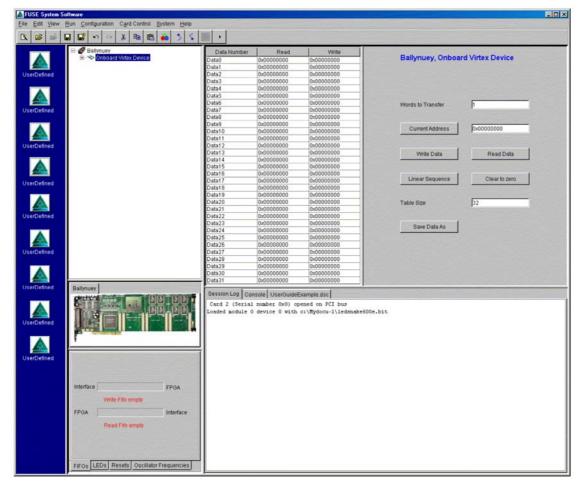

|    | E.II NALLATECH FUSE SOFTWARE SYSTEM                                                                                              | 60       |

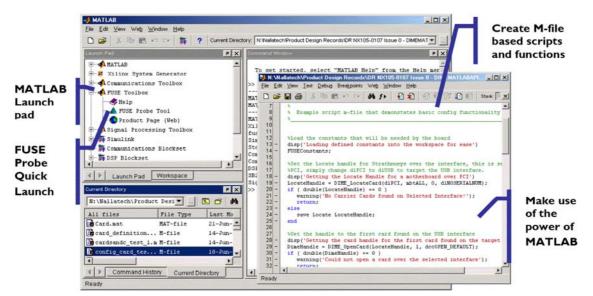

|    | E.III FUSE TOOLBOX FOR MATLAB                                                                                                    | 62       |

| F  | OWNERSHIP STATEMENT AND <i>INTERNAL INTERFACE</i> CODE IMPLEMENTATION AND APPLICATION SUPPORT                                    | 63       |

## 1 INTRODUCTION

Up-to-the-date FPGA circuit technology [1-5] enables effective implementation of millions of reconfigurable logical blocks (LCELLs), hundreds of fast numerical calculations blocks (DSP) [6], a number of embedded microprocessors, multi-gigabit optical transmission lines [7,8] etc. This implementation may done in distributed, multi-channel electronic systems [9,10]. Usage of tens or even thousands of FPGA chips in large measurement-control systems is turning now to an industrial standard. It is possible to realize functional modifications in such modern systems in a faster and much easier way. There is no need to do any changes in the existing hardware structure. There is neither the need to realize a new version of the network or particular devices [12]. The systems of this kind are equipped in extended communication interfaces. These interfaces support full, detailed, remote monitoring, management and diagnostics of particular networked devices [13]. This capability stems from mutual and strong inter-relations between hardware and software layers of the systems. Changes in the hardware layer have to be imaged in the communication layer at the level of hardware (mainly in the FPGA chips) and management software.

This paper presents an idea and examples of applications of a communication interface for FPGA chips called the "*Internal Interface*". This interface simplifies considerably the design process of multi-FPGA chip systems. The interface is automatically implemented in the FPGA chips and in the programming layer of computer based control system. This document is a full theoretical and technical documentation of the *II* communication standard and its implementation. Basing on this documentation the designer may use the *II* technology to build own systems.

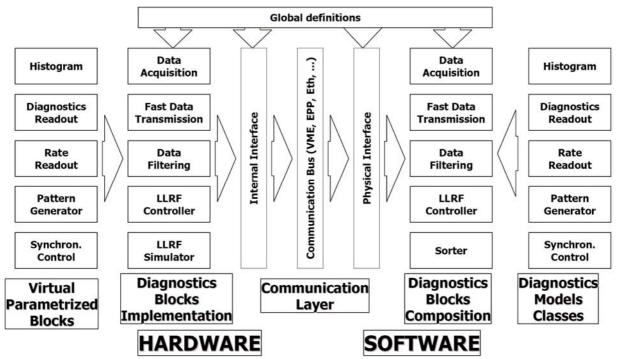

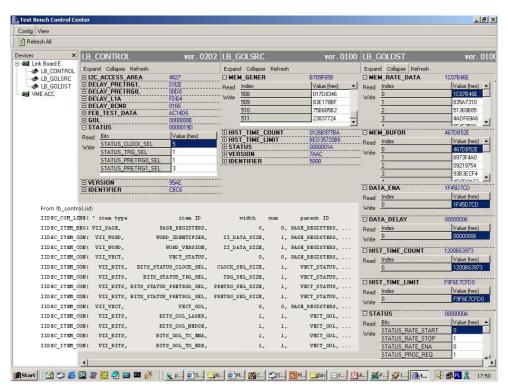

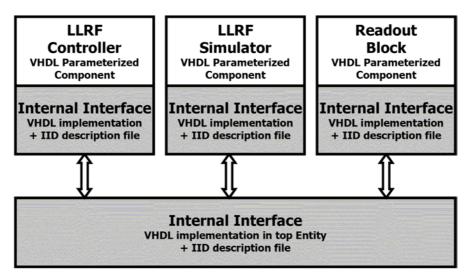

Fig. 1. General structure of the design environment for the Internal Interface.

The *Internal Interface* communication standard (referred in short to as the *II*) was designed originally in 2000-2001 for the electronic system of the RPC Muon Trigger, in the CMS experiment at the LHC accelerator in CERN [14]. Early version of the interface was implemented in the trial PCBs for the TRIDAQ system of BAC detector at ZEUS. The idea of *II* bases on providing automating of design of the local communication interface. The process

is automatic in the hardware (VHDL) layer and in software (C++, MATLAB) layer. A parametric algorithm was implemented to build the address and data areas. This allows for usage optimization of the information exchange area. The method is independent from the communication platform (hardware – PCI, VME, VXI, Ethernet, optical gigalink, etc.).

The usage of the *II* technology is as follows. The project is described in the standardized *II* form using a strictly defined scripting language. The IID file is subject to parallel transformation into the VHDL code and the header file for C++ or MATLAB. This process was shown schematically in fig. 1. The imaging (projection) of the communication layer for hardware functional blocks, implemented in the FPGA chip, is done automatically in the hardware and software layers. This method minimizes the realization time of the project, number of possible errors. It allows for structuring and parameterization of particular functional blocks used in the project.

There are presented the basics of description method for the communication area. These methods are used in the *Internal Interface* technology. The process of building the *II* description is showed from the user point of view and from the side of automatic implementation in the FPGA chip. There are described the following components of the *II* technology:

- the structure of the main *IID* header file,

- user access library functions,

- standard implementation in VHDL language.

There are presented the following examples of the application of *II* library function for:

- single bits,

- registers,

- memory areas,

- project parameterization.

The presented stable release version of the described *Internal Interface* technology is numbered as 1.0 for the following date: 27.11.2005. The *II* interface is under continuous development and the version 2.0 ( to be released in mid 2006) will have the component communication sub-interfaces. In the trial versions it is called the *Component Internal Interface* (*CII*) technology.

## 2 PARAMETRIC HARDWARE BUS

The Internal Interface hardware communication bus is divided to three groups of signals:

- address bus lines II\_addr of the width II\_addr\_width. The address lines are numbered in the range from 0 to II\_addr\_width -1. The youngest line is addressed with the value of 0,

- data bus lines, II\_data of the width II\_data\_width. The data lines are numbered in the range from 0 to II\_data\_width -1. The youngest line is indexed by the value of 0. The bused for the input and output data are separated inside the FPGA chip II\_data\_in and II\_data\_out.

- control lines, realize the access operations and initialization:

- **II\_resetN** the low level forces asynchronous process of the interface initialization,

- **II\_operN** the low level means performing an operation toward the interface,

- **II\_writeN** the low level means the write operation, while high level means the read operation,

- **II\_strobeN** the falling edge means important address in the (address) bus inside the FPGA; the rising edge means important data in the (data) bus during the write operation.

The choice of a peripheral circuit is done by decoding of particular memory area, in many practical system solutions. In such a case, activation of the control line **II\_operN** has to be preceded by (combined with) the decoding of the address space.

Typical solutions of hardware communication buses use bidirectional data bus. Bidirectional buffers have to be used to connect the buses II\_data\_in and II\_data\_out into a common bus II\_data. The direction of data flow is determined by the control line II\_written. Buffer opening is determined by the signal II\_operN.

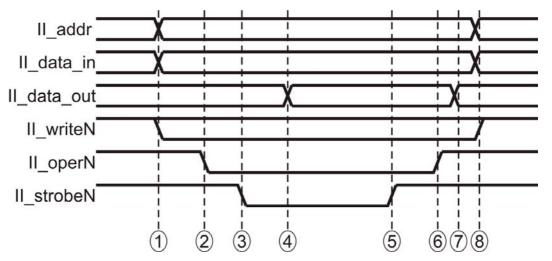

A general time sequence for a single bus operation in the *Internal Interface* for a peripheral FPGA chip is presented in fig. 2.

Fig 2. General time sequence of single operation in the Internal Interface.

A basic access cycle in the *II* consists of eight intermediate steps:

- 1. The *II* controller, before the access cycle begins, sets the value of local address to the address bus **II\_addr**. The control signal **II\_writeN** determines the direction of data distribution. For the read cycle, i.e. for low level of logical state of **II\_writeN**, the value of sent data is set to the data bus **II\_data\_in**. For the write cycle, i.e. for high logical state of **II\_writeN**, the content of **II\_data\_in** bus may be arbitrary, because it is ignored.

- 2. Low level of the control line II\_operN activates the access cycle for a peripheral device. Time period T<sub>1-2</sub> may be omitted. Beginning of the access cycle in time moment T<sub>2</sub> has to be preceded by earlier setting of the transmission direction in the buses buffers, in order to omit the state switching hazards. The activation of low level signal II\_operN has to be done after the address bus value is stabilized inside the receiving FPGA chip. Suggested delay time T<sub>1-2</sub> is approximately 20-25ns.

- 3. The falling edge of signal II\_strobeN is a timing clock for synchronous addressing in the SRAM memories of FPGA chips for the read (i.e. for high logical state of II\_writeN). It is requested that, during time moment T<sub>3</sub>, the state of address lines inside FPGA is stable. The suggested delay time T<sub>2-3</sub> is approximately 15-20ns.

- 4. Input of data onto the II\_data\_out bus is done during the read cycle, i.e. for high logical level of II\_writeN. For synchronous reading of the memory, the time range  $T_{3-4}$  stems form the internal speed of FPGA chip, and typically equals to 20-40ns. For asynchronous reading of static registers, the time range  $T_{2-4}$  is 15-20ns.

- 5. Rising edge of signal II\_strobeN is a timing clock for synchronous writing of data in SRAM memories or static registers in FPGA (i.e. for low logical state of II\_writeN). It is requested that, in time moment T<sub>5</sub>, status of data lines from the bus II\_data\_in inside FPGA is stable. The suggested delay time T<sub>3-5</sub> is approximately 20-30ns.

- 6. Transition of the control line II\_operN to high logical state ends (or interrupts) the access cycle. The buffers of data bus should immediately release the control in the reading cycle (i.e. for high logical state of II\_writeN). It is assumed that the controller *II* performed data reading from the bus II\_data\_out. A typical delay time T<sub>5-6</sub> equals to 20-25ns.

- Setting of the control line II\_operN to the high logical state releases control of the output data bus II\_data\_out. The delay time T<sub>6-7</sub> originates from internal speed of the FPGA chip and is typically 15-20ns.

- 8. Ending of the access cycle by the *II* controller releases the address bus **II\_addr**, the input data bus **II\_data\_in** and sets the control signal **II\_writeN** in high state. The time period T<sub>6-8</sub> may be omitted. It is suggested that, the ending of the access cycle in time moment T<sub>8</sub> is preceded by earlier switching off of the bus buffers, in order to avoid the switching hazards. Suggested delay time T<sub>6-8</sub> is 10-20ns.

The signal **II\_resetN** should be activated with the low level only during the time moment of FPGA chip initialization.

## **3 DECLARATION OF RECORD LIST FOR INTERFACE**

The *Internal Interface* is declared by the *list of records*. A single *record* of the list consists of ordered components. Parameters of a single component are divided to the following categories:

- identifying, enabling precise differentiation of the record (type, name),

- scaling, defining physical dimensions of the record,

- binding, enabling realization of grouping operations,

- access, determining the access rights to the record in write and read modes,

- description, containing information used in programming layer,

| component      | parameter         | description, interpretation                                      |                | remarks        |  |

|----------------|-------------------|------------------------------------------------------------------|----------------|----------------|--|

|                | VII_PAGE          | record of common addressing area                                 |                |                |  |

|                | VII_VECT          | record of common bit vector                                      |                |                |  |

| ItemType       | V <b>II_</b> BITS | record of bit description (i.e. status bit)                      | 0              | see chapt. 3.1 |  |

|                | VII_WORD          | record of word description (i.e. data register)                  |                |                |  |

|                | V <b>II_</b> AREA | record of area description (i.e. memory)                         |                |                |  |

| ItemID         | natural number    | non repeated record identifier                                   | 0              | see chapt. 3.2 |  |

| ItemWidth      | natural number    | data width in record [in bits]                                   | F              |                |  |

| ItemNumber     | natural number    | number of record repetitions (indexing),                         | F              | see chapt. 3.3 |  |

| TCEIIINUIIIDEI | natural number    | (i.e. for VII_AREA number of memory cells)                       | Г              |                |  |

|                |                   | binding identifier ItemID for:<br>VII_BITS is bound to VII_VECT, |                |                |  |

| ItemParentID   | natural number    | Р                                                                | see chapt. 3.4 |                |  |

|                |                   | the rest are bound to VII_PAGE                                   |                |                |  |

| ItemWrType     | VII_WNOACCESS     | component has no write rights from II                            | F              |                |  |

| reenwriype     | VII_WACCESS       | component has write right from II                                | 1              |                |  |

|                | VII_RNOACCESS     | component has no read rights to II                               |                | see chapt. 3.5 |  |

| ItemRdType     | VII_REXTERNAL     | component allows for external reading to II                      | F              |                |  |

|                | VII_RINTERNAL     | Component allows for internal reading to II                      |                |                |  |

| ItemName       | text              | formal name of component                                         | S              |                |  |

|                | VII_FUN_UNDEF     | no identified functional type of component                       |                |                |  |

| ItemFun        | VII_FUN_HIST      | functional type of component - histogram                         | S              | see chapt. 3.6 |  |

|                | VII_FUN_RATE      | functional type of component frequency                           |                | see enapt. 5.0 |  |

| ItemDescr      | text              | component description                                            | S              |                |  |

Tab. 1. List of parameters for a component in the Internal Interface

Table 1 gathers a list of parameters for particulars components of *Internal Interface*. The parameters must appear obligatory, even in the case when their value will be not interpreted for particular component. Thus, the real level of interpretation was marked in table 1 in the following way:

- **O** required parameter, always interpreted,

- F parameter for physical components (VII\_BIT, VII\_WORD, VII\_AREA),

- P parameter for bound components (VII\_VECT, VII\_BITS, VII\_WORD, VII\_AREA),

- S information parameter of programming (ignored during the VHDL analysis),

## 3.1 Record type – ItemType

Structure of the interface is defined by set of records in the list of declarations. The component **ItemType** determines type of a single record. It binds the record to one of two type groups:

- physical, defining real objects of the interface:

- VII\_AREA unified address area of memory type,

- VII\_WORD autonomous bit vector of data word register,

- VII\_BITS set of bits requiring grouping operation VII\_VECT,

- grouping, building common areas (address, data) of respective physical component groups:

- VII\_VECT combines to a common vector the components of type VII\_BITS,

- VII\_PAGE combines components of type VII\_AREA, VII\_WORD, VII\_BITS (ordered previously in VII\_VECT) into a common address area (possessing a unified prefix).

Component **ItemType** precisely determines the rest of parameters of a chosen record. Detailed usage of parameters was described in par. 3.2-3.6.

## 3.2 Record identifier – ItemID

The formal identifier of a record is **ItemID** component. The value of component is arbitrary natural number.

The values of identifiers must not be repeated inside the area of list declaration.

To obtain more readable description, it is suggested that, the identifiers are separate SYMBOLIC CONSTANTS, defined by the user.

Its usage should univocally indicate the subscribed component.

## 3.3 Scaling parameters – ItemWidth, ItemNumber

The scaling parameters describe physical record VII\_BITS, VII\_WORD, VII\_AREA (see chapter 3.1) in two dimensions:

- ItemWidth determines width of the record, expressed in BITS. This parameter is equivalent to a physical number of bits in the data vector std\_logic\_vector. The most significant bit of the vector (MSB) is the bit of the oldest index,

- ItemNumber determines the number of identical, ordered components of the record. The component is chosen by the index from 0 to ItemNumber 1.

The records VII\_BITS and VII\_WORD are interpreted as indexed tables. If the component is used one time only (ItemNumber =1), the index of value 0 is used. For record VII\_AREA, the range of addressing is determined (i.e. the number of memory cells). The addressing range should not be mistaken with the number of addressing lines.

It is suggested to use **0** in the case when these parameters in the record are ignored.

## 3.4 Records grouping – ItemParentID

The grouping relies on adding to a component **ItemParentID** a physical record, which is subject to grouping (see chapter 3.1), the component value **ItemType** respective grouping recode (**VII\_PAGE** or **VII\_VECT**).

#### The grouping record has to be declared earlier.

The grouping of physical records is subject to the following rules:

- VII\_VECT groups only VII\_BITS components in a common data vector. The constructed vector is treated in a similar way as a single element one VII\_WORD.

- VII\_PAGE groups components VII\_BITS, VII\_WORD, VII\_AREA in a common address area a common prefix will be assigned.

It is suggested for the grouping records (containing components VII\_VECT and VII\_PAGE), to use as the grouping parameter their own identifiers.

## 3.5 Access rights to record – ItemWrType, ItemRdType

The access parameters to the physical record determine write right (component ItemWrType) or read right (component ItemRdType) of its data via the physical bus *II*.

The direction of data flow is determined by the signal state II\_writeN (comp. chapter 2). Low signal state II\_writeN means write cycle, i.e. data transfer from the *II* controller to the peripheral FPGA chip. High signal state II\_writeN means read cycle, i.e. transfer of data from the peripheral FPGA chip to the *II* controller.

The access laws are determined for all physical records (i.e. containing components VII\_VECT and VII\_PAGE) in a unified way. The access parameters are determined individually by these components:

- **ItemWrType** for the write cycle:

- VII\_WNOACCESS no write right,

- VII\_WACCESS write right,

- **ItemRdType** for the read cycle:

- VII\_RNOACCESS no right to read,

- VII\_REXTERNAL right to read data from external objects. It was assumed, that in this case, the write right (i.e. ItemwrType= VII\_WACCESS) concerns also data from the external objects.

• VII\_RINTERNAL - right to read data registered internally, on condition that there is assigned the write right (i.e. ItemWrType= VII\_WACCESS). This kind of registering makes accessible only current data for external objects.

Periphery module *II* is only a data retransmitter for external object. It makes the data accessible, on condition the object is addressed on the bus **II\_addr**. The data registration process and data accessibility is done by external object.

It is suggested that the parameters VII\_WNOACCESS and VII\_RNOACCESS are assigned to the grouping records VII\_PAGE and VII\_VECT, for which these parameters are ignored.

## 3.6 Record description – ItemName, ItemFun, ItemDescr

The components of record description (**ItemName**, **ItemFun**, **ItemDescr**) are for information purposes. They are designed for the layer of monitoring software (like C++ or MATLAB) in order to facilitate accessibility and service of particular *II* records.

Description components are ignored at the level of VHDL processing.

The record description components fulfill the following functions:

- **ItemName** contains a TEXT displayed as a name of the component,

- **ItemFun** represents a list of *functional types* of external object:

- VII\_FUN\_UNDEF no functional type defined,

- VII\_FUN\_HIST concerns only VII\_AREA record. It is assumed that the record represents value distribution included in successive words, from 0 to ItemNumber-1, and the counter has the width of the word, or in the range from 0 to 2<sup>ItemWidth</sup> -1,

- VII\_FUN\_RATE concerns only the record VII\_AREA. It is assumed that the record contains the result of frequency counting of ItemNumber signals, and the counter has the width of a word, or the range from 0 to 2<sup>ItemWidth</sup>-1,

- **ItemDescr** contains TEXT displayed as description of the component.

## 4 THE BASICS OF INTERFACE IMPLEMENTATION

Building of physical implementation of the *Internal Interface* in FPGA chip is done automatically in the VHDL language, basing on the *declaration of interface record list* (see chapter 3). This chapter presents basics of *II* building concerning: grouping, fitting to the physical parameters of the communication bus, filling the address area, splitting of data vectors, etc. The final effect of the building process is physical implementation of the interface, i.e. mapping of the addresses, including the grouping requirements, splitting data to parts, when the width is to big for the interface communication bus, etc. An *interface implementation* table is created as a result of the process. The table contains all necessary data on the implementation.

## 4.1 Physical parameters of interface - II\_addr\_width, II\_data\_width

The physical area of *II* is defined by two basic parameters (see chapter 2):

- **II\_addr\_width** the address area is expressed in the number of address lines. It was assumed that the address lines are indexed from 0 to **II\_addr\_width**-1, or the whole address area covers 2<sup>II\_addr\_width</sup> address positions calculated from 0 to 2<sup>II\_addr\_width</sup> -1,

- **II\_data\_width** the width of data vector is expressed in bits. It was assumed that the data lines are indexed from 0 to 0 to **II\_data\_width**-1, or the value of sent data are included in the range from 0 to  $2^{II_{data_width}}-1$ .

## 4.2 Splitting of address area for physical records

The address area for physical records is determined by component type (VII\_AREA, VII\_WORD, VII\_BITS - see. chapter. 3.1) and by scaling parameters (see chapter 3.3). This chapter presents the rules of assigning of address area for particular physical components.

## 4.2.1 Partitioning of VII\_WORD

The parameters defining VII\_WORD determine word length (ItemWidth) and number of components (ItemNumber). Determination of their physical positioning in the *II* space is realized in two steps:

- 1. The number of address positions is determined which are necessary to split the word to partitions, which are not bigger than the width of data bus (II\_data\_width). Successive word partitions are positioned from the most significant for increasing addresses. The last partition of the word may be not full. There is no requirement that the parameter Itemwidth is a multiplication of II\_data\_width.

- 2. The above structural partitioning of a single word is repeated **ItemNumber** times. The words are positioned in the address area one after the other, according to the increasing indexes.

- Example: Distribution of three 18-bit words, designed as W0, W1, W2 (ItemWidth=18, ItemNumber=3) in *II* area of 8-bit data width (II\_data\_width=8). For simplification, it was assumed that the addressing is initialized from the position 0.

| address | <b>D</b> <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | $D_4$ | D <sub>3</sub> | D <sub>2</sub> | <b>D</b> <sub>1</sub> | D <sub>0</sub> | remarks             |

|---------|-----------------------|----------------|----------------|-------|----------------|----------------|-----------------------|----------------|---------------------|

| 0       | W0-7                  | W0-6           | W0-5           | W0-4  | W0-3           | W0-2           | W0-1                  | W0-0           | word for            |

| 1       | W0-15                 | W0-14          | W0-13          | W0-12 | W0-11          | W0-10          | W0-9                  | W0-8           | index 0             |

| 2       |                       |                |                |       |                |                | W0-17                 | W0-16          | macx 0              |

| 3       | W1-7                  | W1-6           | W1-5           | W1-4  | W1-3           | W1-2           | W1-1                  | W1-0           | word for            |

| 4       | W1-15                 | W1-14          | W1-13          | W1-12 | W1-11          | W1-10          | W1-9                  | W1-8           | index 1             |

| 5       |                       |                |                |       |                |                | W1-17                 | W1-16          | mucx 1              |

| 6       | W2-7                  | W2-6           | W2-5           | W2-4  | W2-3           | W2-2           | W2-1                  | W2-0           | word for            |

| 7       | W2-15                 | W2-14          | W2-13          | W2-12 | W2-11          | W2-10          | W2-9                  | W2-8           | word for<br>index 2 |

| 8       |                       |                |                |       |                |                | W2-17                 | W2-16          | muex 2              |

designations: gray fields mean non used data bits.

**comment**: partitioning of a 18-bit indexed word to 8-bit partitions requires reservation of three successive address positions in the *II* area.

#### 4.2.2 Partition of VII\_BITS for vector VII\_VECT

The parameters defining VII\_BITS determine number of bits (ItemWidth) and components (ItemNumber). The record of type VII\_BITS is treated as a unity, of the total dimension ItemWidth\*ItemNumber in bits. It is assumed that the indexed positions are stored successively in the direction of more significant bits. Determination of physical positioning of records VII\_BITS, combined with a single group VII\_VECT (comp. chapter. 3.4), is realized in two steps:

- 1. Calculation of a common bit vector basing on the group VII\_VECT. The records VII\_BITS are positioned in a common vector, in the same succession as their grouping (i.e. according to the succession in the record declaration list), successively from the least significant bits,

- 2. Partitioning of the common vector stems from the real width of the data bus (II\_data\_width). The successive records VII\_BITS are placed one after another and partitioned to the next address word, when the data bus dimension is crossed over (II\_data\_width).

# Crossing the data bus width II\_data\_width by a single record VII\_BIT is a critical error and the *II* implementation is not realized.

| Example: | Positioning  | in 1  | the   | Π   | area  | of    | the   | 8-bit | data | bus | s (II_data_width=8), for |  |

|----------|--------------|-------|-------|-----|-------|-------|-------|-------|------|-----|--------------------------|--|

|          | addressing i | nitia | ted f | ror | n pos | sitio | on 0: |       |      |     |                          |  |

- a table of three bit positions of 2-bit width designated as A0, A1 and A2 (ItemWidth=2, ItemNumber=3),

- a single bit designated as B (ItemWidth=1, ItemNumber=1),

- a table of two positions of 4-bit width designated as C0 and C1 (ItemWidth=4, ItemNumber=2).

| address | D <sub>7</sub> | D <sub>6</sub> | D5   | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | <b>D</b> <sub>1</sub> | $D_0$ | remarks      |

|---------|----------------|----------------|------|----------------|----------------|----------------|-----------------------|-------|--------------|

| 0       |                | В              | A2-1 | A2-0           | A1-1           | A1-0           | A0-1                  | A0-0  | bits A and B |

| 1       | C1-3           | C1-2           | C1-1 | C1-0           | C0-3           | C0-2           | C0-1                  | C0-0  | bit C        |

| 1       | •              | C 11           |      | 11.4           | 0.1.           |                |                       |       |              |

designation: gray fields mean unused bits of data.

**comment**: bit records A and B were placed in a single word. Partitioning to the next word had to be done in the record C.

## 4.2.3 Partition of VII\_AREA

Parameters defining VII\_AREA determine number of cell bits (ItemWidth) and number of cells (ItemNumber). Record of type VII\_AREA is dedicated for implementation of internal SRAM memory blocks in the FPGA. Determination of the physical positioning in the *II* area is done in two steps:

- 1. The number of partitions is determined for the data word width of a cell (ItemWidth) to partitions not bigger than the data bus width (II\_data\_width). Each of calculated partitions of the word is treated nondependently as a memory sub-area, of the number of cells expressed by ItemNumber.

- 2. Memory sub-areas are positioned in the *II* area starting with the least significant toward the most significant partition of data word. Calculation of the base addresses of memory sub-areas fulfills the following criteria:

- Internal addressing of each memory sub-area is done through the least significant lines of the *II* address bus. The address area is from 0 to **ItemNumber-1**,

- Address lines above the area ItemNumber-1 are indexing the successive memory subareas,

- Prefix of the record VII\_AREA indicates of data cell of 0 index for the least significant memory sub-area,

- Total addressing area of a single record VII\_AREA reserves the address lines required for internal addressing and indexing of memory sub-areas.

- Example: Positioning of three memory cells of the word width 20-bits (ItemWidth=20, ItemNumber=3) in the area of *II* of 8-bit data bus (II\_data\_width=8). It was assumed, that the addressing was initiated from the position 7.

| Address | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | remarks              |

|---------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------------|

| 7-15    |                |                |                |                |                |                |                |                | reservation          |

| 16      | A0-7           | A0-6           | A0-5           | A0-4           | A0-3           | A0-2           | A0-1           | A0-0           | address              |

| 17      | A1-7           | A1-6           | A1-5           | A1-4           | A1-3           | A1-2           | A1-1           | A1-0           | memory               |

| 18      | A2-7           | A2-6           | A2-5           | A2-4           | A2-3           | A2-2           | A2-1           | A2-0           | sub-area A           |

| 19      |                |                |                |                |                |                |                |                | sub-area A           |

| 20      | B0-7           | B0-6           | B0-5           | B0-4           | B0-3           | B0-2           | B0-1           | B0-0           | address              |

| 21      | B1-7           | B1-6           | B1-5           | B1-4           | B1-3           | B1-2           | B1-1           | B1-0           |                      |

| 22      | B2-7           | B2-6           | B2-5           | B2-4           | B2-3           | B2-2           | B2-1           | B2-0           | memory<br>sub-area B |

| 23      | -              |                |                |                |                |                |                |                | sub-area D           |

| 24      |                |                |                |                | C0-3           | C0-2           | C0-1           | C0-0           | address              |

| 25      |                |                |                |                | C1-3           | C1-2           | C1-1           | C1-0           |                      |

| 26      |                |                |                |                | C2-3           | C2-2           | C2-1           | C2-0           | memory<br>sub-area C |

| 27      |                |                |                |                |                |                |                |                | Sub-area C           |

| 28-31   |                |                |                |                |                |                |                |                | not used             |

designations: gray fields mean non-used data bits.

**Comment 1**: Partitioning of 20-bit memory word into 8-bit parts requires reservation of two address blocks in the *II* area. Separated memory sub-areas were designated as A, B and C.

- **comment 2**: three memory cells (**ItemNumber=3**) require reservation of two the youngest (least significant) address lines A<sub>0</sub> and A<sub>1</sub>, thus, the last addressing position of each memory sub-area is remains not used.

- **Comment 3**: Choice of a single from three memory sub-areas is done through address lines A<sub>2</sub> and A<sub>3</sub>, thus, the last addressing position of memory sub-area is reserved, but is not unused.

- **Comment 4**: memory prefix was set to 16, because there were reserved addresses up to 7 and it has to indicate to the youngest cell for the youngest memory subarea (i.e. addresses  $A_{3-0}=0$ ). The address position 7 remains unused.

## 4.3 Paging of the address area - VII\_PAGE

Paging of the address area is done through the record binding VII\_AREA, VII\_WORD and VII\_VECT via parameter ItemParentID with respective records of type VII\_PAGE (comp. chapter 3.4). Determination of a physical situation of the pages in the *II* area is realized in two steps:

- 1. Finding of the biggest address area used by a single page, in order to reserve the required number of the youngest bits in the *II* bus. Determination of the addressing range for each page is referenced to the 0 address.

- 2. Assigning the pages, in the succession of their declarations in the record list, numbered indexes from value 0. Assigning of an index for a page is realized by address lines above the area of page addressing.

**Example**: Distribution in the *II* area for 8-bit address bus (**II\_addr\_width**=8):

- Page P1 possessing 5 address positions,

- Page P2 occupying 12 address positions,

- Page P3 possessing 9 address positions.

| Page  |       | Page in        | dexing |                | Ad                                     | dressing | remarks |         |         |  |

|-------|-------|----------------|--------|----------------|----------------------------------------|----------|---------|---------|---------|--|

| index | $A_7$ | A <sub>6</sub> | $A_5$  | A <sub>4</sub> | $A_3 \qquad A_2 \qquad A_1 \qquad A_0$ |          |         |         | Temarks |  |

| 0     | 0     | 0              | 0      | 0              | address                                | es range | Page P1 |         |         |  |

| 1     | 0     | 0              | 0      | 1              | address                                | es range |         | Page P2 |         |  |

| 2     | 0     | 0              | 1      | 0              | address                                | es range | e 0 - 8 |         | page P3 |  |

**Comment 1**: The biggest address area occupies 12 positions, what requires reservation of 4 the youngest address bits  $A_{0-3}$ .

**Comment 2**: The rest of the addressing lines were used to index the pages A<sub>4-7</sub>.

## 4.4 Interface implementation table

The required structure of *Internal Interface* is declared via the list of records (comp. chapter 3). The real image of *II* implementation in FPGA is calculated from the interface implementation table on the basis of the physical parameters of the *II* bus (comp. chapter 4.1).

Change of the *II* physical bus (i.e. parameters **II\_addr\_width** and **II\_data\_width**) does not require redefinition of the user list record. The physical image of interface is built automatically for new parameters of the bus.

component *description*, *interpretation* description parameter Parameter record for interface initialization VII\_PAGE in this chapter VII\_BITS Bit description record ItemType see chapter 3.1 VII\_WORD Bit description record VII\_AREA Area description record ItemID natural number Non-repeatable record identifier see chapter 3.2 ItemParentID natural number Parameter value is not valid omitted ItemWidth natural number Record data width [in bits] see chapter 3.3 ItemNumber natural number Number of record repetitions (indexing), VII WNOACCESS component has no write right from II ItemWrType see chapter 3.5 VII\_WACCESS Component has write right from II **ItemWrPos** Basic position in interface vector for writing natural number in this chapter VII RNOACCESS Component has no read right to II ItemRdType VII\_REXTERNAL see chapter 3.5 Component allows for external read to II VII\_RINTERNAL Component allows for internal read to II ItemRdPos Basic position in interface vector for reading natural number ItemAddrPos natural number Basic position of record address in this chapter Number of address positions of a component in record natural number ItemAddrLen types II\_AREA and VII\_WORD, position of the youngest bit for record type VII\_BITS

Single record of the interface implementation table are ordered components, gathered in table 2:

Tab. 2. List of parameters of component of Internal Interface

The components, with the meaning not changed are only rewritten from the *interface record* list to the *interface implementation* table. Table 2 presents references to respective chapters. The implementation process of *Internal Interface* requires:

- Calculation of addresses values and positioning data for particular physical records,

- Building of interface communication vector for particular physical records,

- Calculation of record parameters for initialization of physical interface implementation.

## 4.4.1 Address parameters – ItemAddrPos, ItemAddrLen

Addressing parameters (ItemAddrPos, ItemAddrLen) for particular physical records (VII\_AREA, VII\_WORD and VII\_BITS) are determined in agreement with the rules of record partitioning (see chapter 4.2) and paging (see chapter 4.3). Partitioning of the address area is performed basing on real parameters of the communication bus (II\_addr\_width and II\_data\_width). Particular addressing components contain:

- ItemAddrPos indicates base address of physical record, i.e. the zero indexed component of this record (see chapter 3.3).

- ItemLenPos for record type VII\_WORD, indicates the number of addresses of a single indexed component (comp. chapter 4.2.1),

- for record type VII\_AREA, indicates the number of memory sub-areas (comp. chapter 4.2.3),

- for record type VII\_BITS, indicates the position of the youngest bit of record (comp. chapter 4.2.2).

#### 4.4.2 Interface vector parameters – ItemWrPos, ItemRdPos

The interface vector parameters (ItemWrPos, ItemRdPos) made accessible for particular physical records (VII\_AREA, VII\_WORD and VII\_BITS) separated communication buses tailored to their dimensions and type. Application of the communication vector plays a role of *logical converter* between physical parameters of the communication bus (II\_addr\_width and II\_data\_width), and particular physical records defined by parameters ItemWidth and ItemNumber.

The process of building of the physical interface requires calculation of the structure of a common communication vector. For the successive physical records (VII\_AREA, VII\_WORD and VII\_BITS) positioned on the list, there are reserved vector partitions according to their types (see chapter 3.1) and the access rights (see chapter 3.5) respectively for the components type ItemWrPos and ItemRdPos:

- ItemWrPos for record type VII\_WORD or VII\_BITS there is reserved a bit range ItemWidth\*ItemNumber,

- for record type VII\_AREA there is reserved a bit range Itemwidth,

- ItemRdPos for record type VII\_WORD or VII\_BITS during the read mode from the external block (ItemRdPos=VII\_RINTERNAL) there is reserved a bit range ItemWidth\*ItemNumber. For the mode of internal reading (ItemRdPos=VII\_RINTERNAL) the vector is the same as the write vector,

- for record type VII\_AREA there is reserved a bit range ItemWidth,

**ItemWrPos** and **ItemRdPos** indicate the youngest bits of the reserved vectors. When there is no reservation of a given vector, the value -1 is inserted to the component.

## 4.4.3 Record of parameters initializing the interface

The record of initializing parameters for the interface is located on the last position in the *interface initialization table* and is of type VII\_PAGE. The next components of record are gathered in table 2 and contain important parameters:

- Itemwidth data bus width (parameter II\_data\_width),

- ItemNumber address bus width (parameter II\_addr\_width),

- ItemAddrPos total length of interface vector (comp. chapter 4.4.2),

- ItemAddrLen- the highest physical address used in interface (comp. chapter 4.4.1).

## 5 INTERFACE IMPLEMENTATION

Implementation of the *Internal Interface* bases on placing in the code standardized service blocks (like building, initialization, control of communication bus, etc.) and usage of library functions and procedures enabling the user a cooperation with the interface.

Further part of the chapter assumes, that the dimension of address bus is determined by the parameter II\_addr\_width, and the data bus is determined by II\_data\_width.

The abbreviations and types of the variables used in declarations and functions are gathered and explained in appendix A.I.

## 5.1 Library functions

• Library functions of interface: (all declarations are gathered in appendix A.II.6):

VIINameConv ( \_NAME\_ :TS) return TS

where:

• \_NAME\_ is a description name of record (see chapt. 3.6)

Function returns type TS of the length VII\_ITEM\_NAME\_LEN (see appendix A.II.3).

VIIDescrConv ( \_DESCR\_ :TS) return TS

where:

• \_ DESCR \_ is description of component (see chapt. 3.6)

Function returns type TS of the length  $VII\_ITEM\_DESCR\_LEN$  (see appendix A.II.3).

• requested library functions: (all declarations are gathered in app. A.I.4):

pow2 (\_VAL\_ :TN) return TN

where:

• \_VAL\_ is a value of natural number type, Function returns the result of: 2<sup>-VAL\_</sup> as natural value. **Caution:** This function has to be used instead of power operator ^.

TVLcreate (\_VAL\_ :TN) return TVL

where:

• \_VAL\_ is a value of natural type.

Function returns a minimal number of bits necessary to write the value of \_VAL\_. **Caution:** The result of function has to be interpreted as a length of vector TSLV

#### SLVMax (\_VAL\_ :TN) return TN

where:

• \_VAL\_ is a value of natural type

Function returns maximal natural value which can be obtained from vector of the length \_VAL\_ bits.

**Caution:** Formally, the function returns the result of expression:  $2^{-VAL} - 1$ .

## 5.2 Standard initialization of interface

Standard initialization of the Internal Interface requires performing of the following steps:

- Processing of *record declaration list* (comp. chapt. 3) to the physical implementation with the function **TVIICreate** to obtain the form of *interface implementation table* (comp. chapt.4.4). The table contains all necessary implementation data for the interface.

- Building, with the aid of function TVII, of three intermediate vectors IIVecInt, IIVecAll and IIVecEna type TSLV enabling communication with the *II*:

#### example:

constant **IIPar** :TVII := TVIICreate(VIIItemDeclList, II\_addr\_width, II\_data\_width); signal **IIVecInt**, **IIVecAII**, **IIVecEna** :TSLV(VII(IIPar)'high downto VEC\_INDEX\_MIN);

Caution: - VIIItemDeclList is a name of a declaration list (comp. chapt. 3),

- Constant IIPar is an *interface implementation table* (comp.chapt.4.4).

The intermediate vectors are designed to forward the following information:

- **IIVecInt**: stores internal states of *II* registers (see chapt. 3.5),

- **IIVecAII**: contains all states of *II* signals,

- **IIVecEna**: value '1' denotes that particular signal is made accessible by the *II* respectively in the write or read mode.

**Caution:** information of writing to the internal register of the *II* is not accessible.

• Library functions: (all declarations are gathered in append. A.II.7):

TVIICreate ( \_LISTA\_ :TVIIItemDeclList; \_ADDR\_WIDTH\_, \_DATA\_WIDTH\_ :TVL) return TVII

where:

- \_LISTA\_ is created list of *II* components declarations,

- \_ADDR\_WIDTH\_ determines number of bits for interface address bus,

- \_DATA\_WIDTH\_ determines number of bits for interface data bus,

Function returns physical implementation of interface as table type TVII (comp. chapt.4.4).

#### VII ( \_IIPAR\_ :TVII) return TSLV

where:

• \_IIPAR\_ is a list of physical implementation of interface,

Function returns an empty intermediate vector type TSLV of dimension originating from current implementation.

## 5.3 Standard service of interface

Standard service of Internal Interface requires the following actions:

- Service process of internal registers stored in vector IIVecInt,

- Current actualization of vector **IIVecAll** originating from current state of data distribution via the *II* bus from internal blocks and data stored in vector **IIVecInt**,

- Current actualization of vector **IIVecEna** originating from current state of data distribution via the *II* bus,

- Calculation of output data from the *II* via the bus **II\_data\_out**.

example:

```

process ( II_resetN, II_strobeN )

begin

if ( II_resetN = '0' ) then

IIVecInt <= IIReset ( IIVecInt, IIPar );</pre>

elsif ( II_strobeN'event and II_strobeN = '1' ) then

if ( II_operN = '0' and II_writeN = '0' ) then

IIVecInt <= IISave( IIVecInt, IIPar, II_addr, II_data_in );</pre>

end if:

end if;

end process;

IIVecEna <= IIEnable( IIPar, II_operN, II_writeN, II_addr );</pre>

IIVecAll <= IIWrite( IIVecInt, IIPar, II_addr, II_data in )</pre>

or IIConnPutWordData(IIVecInt, IIPar, ....)

or IIConnPutWordtab( IIVecInt, IIPar, .... )

or IIConnPutBitsData(IIVecInt, IIPar, ....)

or IIConnPutBitsTab( IIVecInt, IIPar, .... )

or IIConnPutAreaData(IIVecInt, IIPar, ....)

or IIConnPutAreaMData(IIVecInt, IIPar, ....)

or .....;

```

II\_data\_out <= IIRead( IIVecAll, IIPar, II\_addr );</pre>

Vector **IIVecAll** is calculated in common by standard service operations of the interface and by the user. The user, via successive OR operations connects all data from external objects (declared as **VII\_REXTERNAL**).

**Caution:** Connection to vector **IIVecAll** of data from external objects is done ONLY with the aid of library functions respectively to the type of object.

• Library functions of interface service: (declarations were included in append. A.II.8):

IIReset ( \_VEC\_ : TSLV; \_IIPAR\_ :TVII) return TSLV

where:

- \_VEC\_ represents interface IIVecInt (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt 5.2),

Function returns vector \_VEC\_ with zeroed internal registers.

IISave ( \_VEC\_ : TSLV; \_IIPAR\_ :TVII; \_ADDR\_, \_DATA\_IN\_ :TSLV) return TSLV

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ADDR\_ is interface address bus,

- \_DATA\_IN\_ is interface input data bus.

Function returns actualization of the internal registers vector \_VEC\_.

#### IIEnable ( \_IIPAR\_ :TVII; \_ENABLE\_, \_WRITE\_ :TSL; \_ADDR \_ :TSLV) return TSLV

where:

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ENABLE\_ low level enable signal (see chapt. 2),

- \_WRITE\_ is interface data direction signal (see chapt. 2),

- \_ADDR\_ is interface address bus.

Function returns access vector (accessing is denoted by '1').

#### IIWrite (\_VEC\_ : TSLV; \_IIPAR\_ :TVII; \_ADDR\_, \_DATA\_IN :TSLV) return TSLV

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ADDR\_ is interface address bus,

- \_DATA\_IN\_ is interface input data bus.

Function returns vector \_VEC\_ supplemented with information from interface bus.

#### IIRead (\_VEC\_ : TSLV; \_IIPAR\_ :TVII; \_ADDR\_ :TSLV) return TSLV

where:

- \_VEC\_ represents interface vector IIVecInt (see chapt. 5.2),

- \_IIPAR\_ is interface implementation table (see chapt. 5.2),

- \_ADDR\_ is interface address bus.

Function returns interface output data or the high state.

• Library functions of object service: (declarations are presented in app. A.II.9- A.II.11):

IIConnPutWordData (\_VEC\_: TSLV; \_IIPAR\_:TVII; \_ITEM\_ID\_:TN; \_POS\_:TVI; \_VAL\_:TSLV) return TSLV

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is interface implementation table (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_ WORD (see chapt. 3.2),

- \_POS\_ index of object components (see chapt. 3.3),

- \_VAL\_ transferred value of object component.

Function returns vector \_VEC\_ filled with the value of object component \_VAL\_.

IIConnPutWordTab (\_VEC\_ : TSLV; \_IIPAR\_ :TVII; \_ITEM\_ID\_ :TN; \_VAL\_ :TSLV) return TSLV

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is interface implementation table (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_ WORD (see chapt. 3.2),

- \_VAL\_ transferred value of the whole object component in a form of vector.

Function returns vector \_VEC\_ filled with the value of the whole object component \_VAL\_.

IIConnPutBitsData (\_VEC\_: TSLV; \_IIPAR\_:TVII; \_ITEM\_ID\_:TN; \_POS\_:TVI; \_VAL\_:TSLV) return TSLV

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_BITS (see chapt. 3.2),

- \_POS\_ index of object components (see chapt. 3.3),

- \_VAL\_ transferred value of object component.

Function returns vector \_VEC\_ filled with the value of object component \_VAL\_.

#### IIConnPutBitsTab (\_VEC\_: TSLV; \_IIPAR\_:TVII; \_ITEM\_ID\_:TN; \_VAL\_:TSLV) return TSLV

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_BITS (see chapt. 3.2),

- \_VAL\_ transferred value of the whole object component in a form of vector.

Function returns vector \_VEC\_ filled with the value of the whole object \_VAL\_.

| IIConnPutAreaData (_VEC_ | : TSLV; _IIPAR_ | _ : <b>TVII</b> ; _ITI | EM_ID_ :TI | N; _VAL_ :TSLV) |

|--------------------------|-----------------|------------------------|------------|-----------------|

| return <b>T</b>          | SLV             |                        |            |                 |

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_BITS (see chapt. 3.2),

- \_VAL\_ transferred value of the memory cell in a form of vector.

Function returns vector \_VEC\_ filled with the value of the whole object \_VAL\_.

#### IIConnPutAreaMData (\_VEC\_: TSLV; \_IIPAR\_:TVII; \_ITEM\_ID\_:TN; \_VAL\_:TSLV) return TSLV

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is interface implementation table (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_AREA (see chapt. 3.2),

- \_VAL\_ transferred value of the memory cell in a form of vector.

Function returns vector \_VEC\_ filled with the content of object \_VAL\_ in the dimension not smaller than the width of data bus (II\_data\_width).

## 5.4 User functions

User functions, for each type of physical object, enable the following operations (the character string Xxxx means respectively Word, Bits, Area):

- IIConnGetXxxxData accessing of current data of component.

- **Caution:** Does not concern type VII\_AREA because this object is directly connected to the data and address bus in the range originating from the dimension of the component (see chapt. 4.2.3).

- **Caution:** The data of record internally registered may be accessed directly. The data of external object are important only during the moment of its writing by the *II* bus. They require confirmation of validity by the use of function IIConnGetXxxxWriteEna.

- **IIConnGetXxxxEnable** taking of information of accessibility (for write or read)

- **Caution:** Data of the record registered internally made accessible the information of the validity of data only for the read operation.

- IIConnGetXxxxWriteEna taking of information of accessibility during write. Caution: The data of registered record does not provide this information.

- IIConnGetXxxxReadEna taking of information of availability during write.

- IIConnGetXxxxSave taking of information of conditional write cycle status II\_strobeN

• Library functions of data taking: (declarations included in appendix A.II.9- A.II.11):

#### IIConnGetWordData (\_VEC\_: TSLV; \_IIPAR\_:TVII; \_ITEM\_ID\_:TN; \_POS\_:TVI) return TSLV

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_WORD (see chapt. 3.2),

- \_POS\_ index of object components (see chapt. 3.3),

Function returns actual value of object component.

#### IIConnGetWordData (\_DVEC\_, \_EVEC\_ : TSLV; \_IIPAR\_ :TVII; \_ITEM\_ID\_ :TN; \_POS\_ :TVI; \_DATA\_ : TSLV) return TSLV

where:

- \_DVEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_EVEC\_ represents interface vector **IIVecEna** (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_WORD (see chapt. 3.2),

- \_POS\_ index of object components (see chapt. 3.3),

- \_DATA\_ actual data of external object component,

Function returns modified actual value of external object component.

#### IIConnGetBitsData (\_VEC\_: TSLV; \_IIPAR\_:TVII; \_ITEM\_ID\_:TN; \_POS\_:TVI) return TSLV

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_BITS (see chapt. 3.2),

- \_POS\_ index of object components (see chapt. 3.3),

Function returns actual value of object component.

• Library functions of access: (declarations included in appendix A.II.9- A.II.11):

#### IIConnGetWordEnable (\_VEC\_ : TSLV; \_IIPAR\_ :TVII; \_ITEM\_ID\_ :TN; \_POS\_ :TVI; \_WRITE\_ :TSL) return TSLV

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_WORD (see chapt. 3.2),

- \_POS\_ index of object components (see chapt. 3.3),

- \_WRITE\_ is interface data direction signal (see chapt. 2),

Function returns actual state of data accessibility to object component for both types of operations (write and read). When a chosen bit of object is accessible, then in the returned vector this bit has value '1'.

**Caution:** Assumption of the above solution, stems from the partitioning possibility of record type VII\_WORD to parts (comp. chapter 4.2.1). Then, only the chosen part of record will possess the bits set to '1', and the rest of bits will remain set to '0'.

## IIConnGetBitsEnable (\_VEC\_ : TSLV; \_IIPAR\_ :TVII; \_ITEM\_ID\_ :TN; \_WRITE\_ :TSL) return TSL

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_BITS (see chapt. 3.2),

- \_WRITE\_ is interface data direction signal (see chapt. 2),

Function returns actual accessibility status of the component: '1' – component is accessible.

**Caution:** Assumed solution stems from that the component type VII\_BITS must not be divided to partitions (comp. chapter 4.2.2). Access concerns all positions of the object.

IIConnGetAreaEnable (\_VEC\_ : TSLV; \_IIPAR\_ :TVII; \_ITEM\_ID\_ :TN; \_WRITE\_ :TSL) return TSL

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_AREA (see chapt. 3.2),

- \_WRITE\_ is interface data direction signal (see chapt. 2),

Function returns actual accessibility status: '1' – component is accessible.

**Caution:** Assumed solution stems from that the component type AREA is treated as a unity not to be divided (comp. chapter 4.2.3).

#### IIConnGetWordWriteEna

IIConnGetWordReadEna (\_VEC\_ : TSLV; \_IIPAR\_ :TVII; \_ITEM\_ID\_ :TN; \_POS\_ :TVI) return TSLV

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapt. 5.2),

- \_IIPAR\_ is interface implementation table (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_WORD (see chapt. 3.2),

- \_WRITE\_ is interface data direction signal (see chapt. 2),

Function acts identically as IIConnGetWordEnable, respectively for write operation (IIConnGetWordWriteEna) or read (IIConnGetWordReadEna).

#### IIConnGetBitsWriteEna

IIConnGetBitsReadEna (\_VEC\_: TSLV; \_IIPAR\_: TVII; \_ITEM\_ID\_: TN) return TSL

where:

- \_VEC\_ represents interface vector IIVecEna (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_AREA (see chapt. 3.2),

Function acts identically as IIConnGetBitsEnable respectively for write operation (IIConnGetBitsWriteEna) or read (IIConnGetBitsReadEna).

#### IIConnGetAreaWriteEna

#### IIConnGetAreaReadEna (\_VEC\_: TSLV; \_IIPAR\_: TVII; \_ITEM\_ID\_: TN) return TSL

where:

- \_VEC\_ represents interface vector **IIVecEna** (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_AREA (see chapt. 3.2),

Function acts identically as IIConnGetAreaEnable respectively for writing operation (IIConnGetAreaWriteEna) or reading (IIConnGetAreaReadEna).

IIConnGetWordSave (\_VEC\_: TSLV; \_IIPAR\_:TVII; \_ITEM\_ID\_:TN; \_POS\_:TVI; \_SAVE\_:TSL) return TSLV

where:

- \_VEC\_ represents interface vector IIVecEna (see chapt. 5.2),

- \_IIPAR\_ is *interface implementation table* (see chapt. 5.2),

- \_ITEM\_ID\_ is identifier of object type VII\_AREA (see chapt. 3.2),

- \_POS\_ index of object components (see chapt. 3.3),

- \_SAVE\_ is signal II\_strobeN (see chapter 2),

Function returns '1' for active state of the signal (i.e. low state) \_SAVE\_ for these bits of object data vector, which are actually accessible for writing (comp. acting of function IIConnGetWordWriteEna). The rest of bits are set continuously for '0'.

| IIConnGetBitsEnable (_VEC_ : | : TSLV; _IIPAR_ | _ : <b>TVII</b> ; _l <sup>-</sup> | TEM_ID_ | _: <b>TN</b> ;_ | _SAVE_ | :TSL) |

|------------------------------|-----------------|-----------------------------------|---------|-----------------|--------|-------|

| return TS                    | SL              |                                   |         |                 |        |       |

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapter 5.2),

- \_IIPAR\_ is interface implementation table (see chapter 5.2),

- \_ITEM\_ID\_ is object identifier of type VII\_BITS (see chapter 3.2),

- \_SAVE\_ original II\_strobeN signal (see chapter 2),

Function returns '1' for active (low) state of signal \_SAVE\_ under the condition that the component was made accessible for writing (compare result of function IIConnGetBitsWriteEna).

IIConnGetAreaEnable (\_VEC\_: TSLV; \_IIPAR\_:TVII; \_ITEM\_ID\_:TN; \_SAVE\_:TSL) return TSL

where:

- \_VEC\_ represents interface vector **IIVecInt** (see chapter 5.2),

- \_IIPAR\_ is interface implementation table (see chapter 5.2),

- \_ITEM\_ID\_ is object identifier of type VII\_BITS (see chapter 3.2),

- \_SAVE\_ original II\_strobeN signal (see chapter 2),

Function returns '1' for active (low) state of signal \_SAVE\_ under the condition that the component was made accessible for writing (compare result of function IIConnGetAreaWriteEna).

## 6 EXAMPLE OF INTERFACE IMPLEMENTATION

An example of *Internal Interface* implementation was presented in this chapter. This example is considered from the point of view of several basic aspects:

- Definition of declaration list of records for the tested interface (see chapter 3)

- Area structure analysis of the *II*. The area structure is positioned in implementation table (see chapter 4)

- Suggested structure of VHDL file and basics of usage of library functions (see chapter 5)

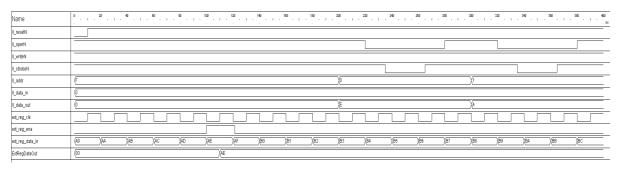

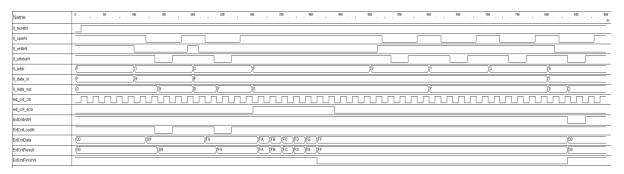

- Discussion of results of functional simulation

To keep the implementation readable, the example was confined to a few components.

## 6.1 Project of records for interface declaration list

The test project assumes the following working parameters:

- Interface parameters: II\_ADDR\_WIDTH=4, II\_DATA\_WIDTH=4,

- User bus parameters: TEST\_WIDTH=8.

Table 3 gathers record declarations for test interface (see tab. 1). There were presented shortly access rights. The description parameters were omitted (comp. chapter 3.6). Description parameters are not important for VHDL processing.

| Page      | Vector   | Type_Item | Width         | Number | Access  | Comment              |

|-----------|----------|-----------|---------------|--------|---------|----------------------|

|           |          | WORD CHK  | II_DATA WIDTH | 1      | Ext. RO | Control sum          |

|           |          |           |               | 1      |         | readout              |

|           |          | WORD STAT | II_DATA WIDTH | 1      | Ext. RO | Constant value       |

|           |          | WORD_STAT |               | T      | LXL. KU | readout              |

|           |          | WORD_INT  | II_DATA_WIDTH | 2      | Int. RW | 2 internal registers |

| PAGE_REG  |          | WORD_EXT  | TEST_WIDTH    | 1      | Ext. RW | External register    |

|           | VECT_INT | BITS_INT1 | 2             | 1      | Int. RW | 2 internal bits      |

|           | VECT_INT | BITS_INT2 | 1             | 1      | Int. RW | 1 internal bit       |

|           | VECT_EXT | BITS_EXT1 | 1             | 1      | Ext. WO | 1 external bit       |

|           | VECT_EXT | BITS_EXT2 | 2             | 1      | Ext. RW | 2 external bits      |

| PAGE_AREA |          | AREA_EXT  | TEST_WIDTH    | 3      | Ext. RW | 3 cell memory        |

Tab. 3. Declaration set of records for test interface

designations: - gray fields mean invalid parameters,

- Ext. - external register, Int. - internal register,

- RO- reading only WO writing only, RW full access.

- **comment 1**: Records of type VII\_WORD and VII\_BITS are positioned in page PAGE\_REG, record of type VII\_AREA are positioned in page PAGE\_AREA.

- **comment 2**: Records of type VII\_WORD were declared with parameterized width parameters (Itemwidth), while records of type VII\_BITS have only constant dimensional parameters.

- **comment 3**: Record of type VII\_WORD of identifier WORD\_EXT and record of type VII\_AREA of identifier AREA\_EXT have the word width bigger than the data bus and, thus, require partitioning.

## 6.2 Calculation of interface implementation table

Calculation of the implementation table determines:

- Required address area of interface together with its positioning inside particular records and positioning of records inside the data bus,

- Value and total length of the communication vector, i.e. positioning in its area the communication buses for particular records.

Table 4 gathers calculated parameters of implementation table for test interface. Repeated parameters from interface record declaration were omitted (see. tab. 2).

| Type_Item | Width | Number | Access  | ItemWrPos | ItemRdPos | ItemAddrPos | ItemAddrLen |

|-----------|-------|--------|---------|-----------|-----------|-------------|-------------|

| WORD_CHK  | 4     | 1      | Ext. RO | -1        | 0         | 0           | 1           |

| WORD_STAT | 4     | 1      | Ext. RO | -1        | 4         | 1           | 1           |

| WORD_INT  | 4     | 2      | Int. RW | 8         | 8         | 2           | 1           |

| WORD_EXT  | 8     | 1      | Ext. RW | 16        | 24        | 4           | 2           |

| BITS_INT1 | 2     | 1      | Int. RW | 32        | 32        | 6           | 0           |

| BITS_INT2 | 1     | 1      | Int. RW | 34        | 34        | 6           | 2           |

| BITS_EXT1 | 1     | 1      | Ext. WO | 35        | -1        | 7           | 0           |

| BITS_EXT2 | 2     | 1      | Ext. RW | 36        | 38        | 7           | 1           |

| AREA_EXT  | 8     | 3      | Ext. RW | 40        | 44        | 8           | 2           |

| Interface | 4     | 4      | -       | -1        | -1        | 48          | 15          |

Tab. 4. Collection of record declarations for test interface.

designation: - gray fields denote initializing record of the interface (see. chapt. 4.4.3),

- Ext. – external register, Int. – internal register,

- RO- read only, WO – write only, RW – full access.

Table. 5 presents physical distribution of components in address area and data in the *Internal Interface* communication bus.

| ll_Addr |             | II_D  | compon     | ent        |                 |       |

|---------|-------------|-------|------------|------------|-----------------|-------|

| (A3-A0) | D3          | D2    | D1         | D0         | identifier      | index |

| 0       | bit 3       | bit 2 | bit 1      | bit 0      | WORD_CHK        | 0     |

| 1       | bit 3       | bit 2 | bit 1      | bit 0      | WORD_STAT       | 0     |

| 2       | bit 3       | bit 2 | bit 1      | bit 0      | WORD_INT 0<br>1 |       |

| 3       | bit 3       | bit 2 | bit 1      | bit 0      |                 |       |

| 4       | bit 3       | bit 2 | bit 1      | bit 0      | WORD_EXT 0      |       |

| 5       | bit 7       | bit 6 | bit 5      | bit 4      | WORD_EXT        | 0     |

| 6       |             |       | bit 1      | bit 0      | BITS_INT1       | none  |

| 0       |             | bit 0 |            |            | BITS_INT2       | none  |

| 7       |             |       |            | bit 0      | BITS_EXT1       | none  |

| 1       |             | bit 1 | bit 0      |            | BITS_EXT2       | none  |

| 8-11    | bit 3       | bit 2 | bit 1      | bit 0      | AREA_EXT        |       |

| 0-11    | DIL 3 DIL 2 |       | Sit 0      | Sub-area 0 | none            |       |

| 12-15   | bit 7       | bit 6 | bit 5      | bit 4      | AREA_EXT        | none  |

| 12-10   |             |       | Sub-area 1 |            |                 |       |

Tab. 5. Collection of record declaration for test interfacedesignations:- gray fieldsgray fields

**comment 1**: The biggest address used in the implementation is 13. Calculation of addresses starts always from the position 0.

**comment 2**: The width of interface vector is 48 bits.

|                        | 0.1 1      | · ·              | 1 1 1 1 1       |

|------------------------|------------|------------------|-----------------|

| ( 'alculated structure | of the bug | vector is preser | nted in table 6 |

| Calculated structure   | or the bus |                  | neu m table 0.  |

|                        |            |                  |                 |

| cycle               | range | e [bits] | component      |       |  |

|---------------------|-------|----------|----------------|-------|--|

| Cycle               | MSL   | LSB      | identifier     | index |  |

| Reading             | 3     | 0        | WORD_CHK       | 0     |  |

| Reading             | 7     | 4        | WORD_STAT      | 0     |  |

| Writing and reading | 11    | 8        | WORD INT       | 0     |  |

|                     | 15    | 12       |                | 1     |  |

| Writing             | 23    | 16       | WORD EXT       | 0     |  |

| Reading             | 31    | 24       | WORD_EXT       | 0     |  |