# Technical University of Lodz Departament of Microelecronics and Computer Science

MSc Thesis

# Distributed System for Designing Reliable Digital Systems Using Genetic Algorithms

Tomasz Norek

Student number: 106121

Supervisor: Grzegorz Jabłoński, PhD

Auxiliary Supervisor: **Dariusz Makowski, MSc**

Łódź, 2005

# Streszczenie

Układy programowalne stają się coraz ważniejsze w dzisiejszych zastosowaniach elektronicznych. Ich wszechstronność jest coraz częściej wykorzystywana już nie tylko do testowania prototypowych rozwiązań, ale nawet do produkcji urządzeń w małych seriach, gdzie koszt wytworzenia specyficznego układu krzemowego znacząco wpłynałby na cenę ostatecznego produktu. Ta uniwersalność jest także źródłem słabości układów programowalnych, ponieważ stają się one wrażliwe na zjawiska zachodzące w krzemie pod wpływem promieniowania. Praca ta opisuje jedną z technik zapobiegania negatywnym skutkom takich zjawisk – użycie algorytmów genetycznych do zaprojektowania takiej konfiguracji układu programowalnego, która mimo zmian powodowanych przez promieniowanie w niej samej, zachowa prawidłową funkcjonalność układu. Ponieważ symulacja układów programowalnych jest zadaniem wymagającym dużych mocy obliczeniowych, praktyczna część pracy obejmuje budowę rozproszonego systemu do obliczeń genetycznych i użycie tego systemu do przeprowadzenia symulacji weryfikujących przydatność wyżej wspomnianej techniki. System rozproszony okazał się bardzo dobrze spełniać swoje zadanie - dał możliwość wykorzystania dużej mocy obliczeniowej bez żadnych dodatkowych kosztów. Symulacje przeprowadzone przy użyciu systemu pozwoliły na zmniejszenie prawdopodobieństwa powstania wadliwej konfiguracji przykładowego układu ponad 50-krotnie. Praca zawiera również wyjaśnienie mechanizmów oddziaływania różnych typów promieniowania z układami krzemowymi, opis technik zapobiegania negatywnym skutkom takiego oddziaływania, opis typów programowalnych, opis możliwych skutków układów jakie może wywołać promieniowanie w tych układach (rozdział 2), wyjaśnienie zasady działania algorytmów genetycznych (rozdział 3). Struktura systemu rozproszonego użytego do symulacji wraz z krótką charakterystyką środowisk używanych do budowy systemów rozproszonych została przedstawiona w rozdziale 4. Rozdział 5 prezentuje wyniki uzyskane podczas symulacji. Rozdział 6 podsumowuje wyniki, zawiera wnioski dotyczące praktycznego użycia zaprezentowanego rozwiązania.

# **Table of Contents**

| STRESZ       | CZENIE                                                           | 2  |

|--------------|------------------------------------------------------------------|----|

| 1. INT       | <b>FRODUCTION</b>                                                | 5  |

| 1.1.         | PROJECT GOALS                                                    | 6  |

| 2. IMI       | PACT OF RADIATION ON PROGRAMMABLE CIRCUITS                       | 7  |

|              |                                                                  |    |

| 2.1.<br>2.2. | RADIATION AND MATTER INTERACTION<br>RADIATION EFFECTS IN SILICON |    |

| 2.2.         |                                                                  |    |

| 2.2.         |                                                                  |    |

| 2.2.         | 2. Single Event Effects                                          |    |

| 2.3.         | PROGRAMMABLE CIRCUITS                                            |    |

| 2.7.         | SPLDs                                                            |    |

|              | CPLDs                                                            |    |

|              | FPGAs                                                            |    |

|              | Radiation influence on the programmable circuits                 |    |

| 2 4 101      |                                                                  |    |

|              | PLICATION OF GENETIC ALGORITHMS IN FAULT-TOLERANT<br>IT DESIGN   | 35 |

|              |                                                                  |    |

| 3.1.         | GENETIC ALGORITHMS                                               |    |

| 3.1.         |                                                                  |    |

| 3.1.         | · · · · · · · · · · · · · · · · · · ·                            |    |

| 3.1.         |                                                                  |    |

| 3.1.         |                                                                  |    |

|              | Random Number Generator                                          |    |

|              | Chromosome representation                                        |    |

|              | Fitness function<br>Fitness scalers                              |    |

|              | Chromosome cross-over operators                                  |    |

|              | Evolution program                                                |    |

|              |                                                                  |    |

| 4. DIS       | STRIBUTED SYSTEM                                                 | 74 |

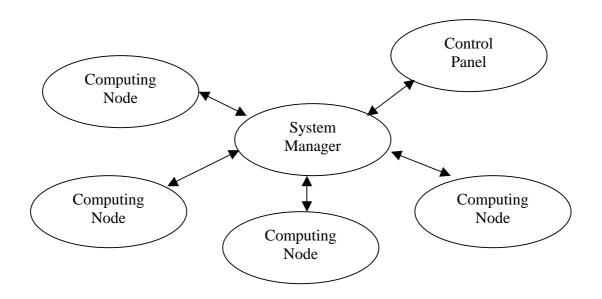

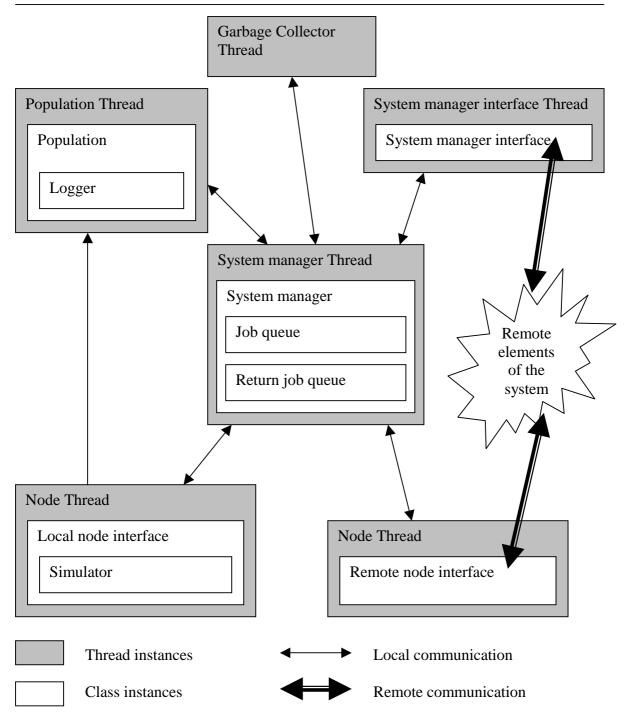

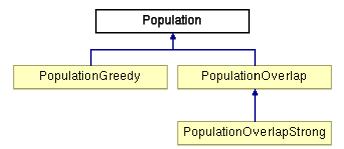

| 4.1.         | System Structure                                                 | 75 |

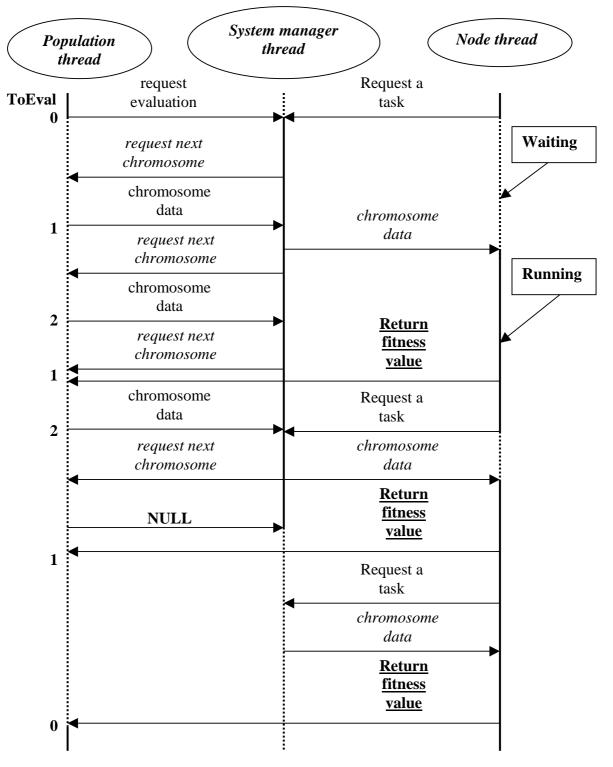

|              | System Manager                                                   | 75 |

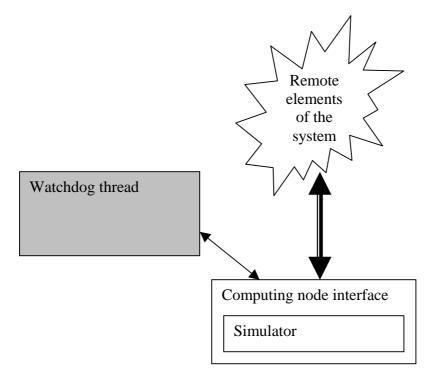

|              | Computing node                                                   | 80 |

|              | Control panel                                                    | 81 |

| 4.2.         | DISTRIBUTED ENVIRONMENTS                                         | 82 |

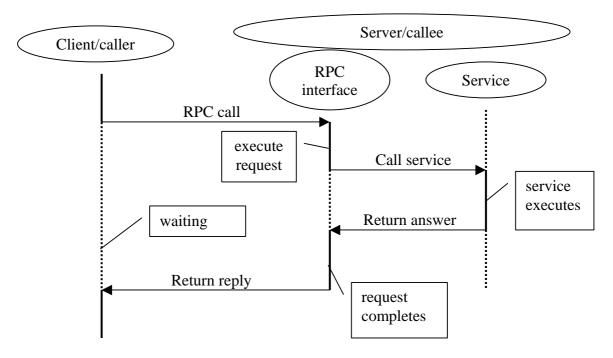

|              | Remote Procedure Call (RPC)                                      |    |

|              | Distributed Component Object Model (DCOM)                        |    |

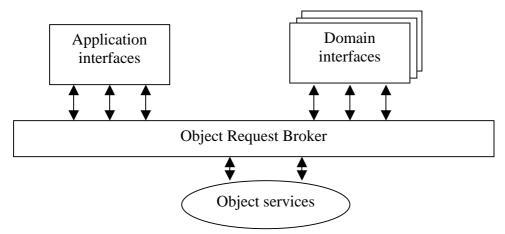

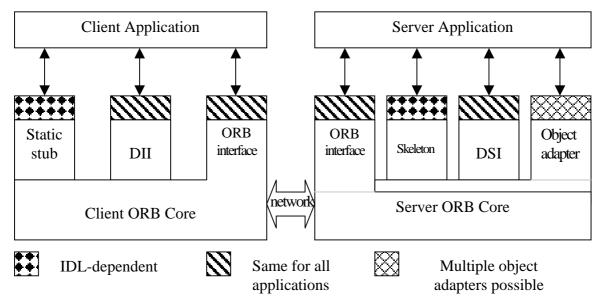

|              | Common Object Request Broker Architecture (CORBA)                |    |

|              | Remote Method Invocation (RMI)                                   |    |

|              | Choice of distributed object environment                         |    |

|              | CORBA interfaces                                                 | 90 |

| 5.  | SIMULATION RESULTS                                |  |

|-----|---------------------------------------------------|--|

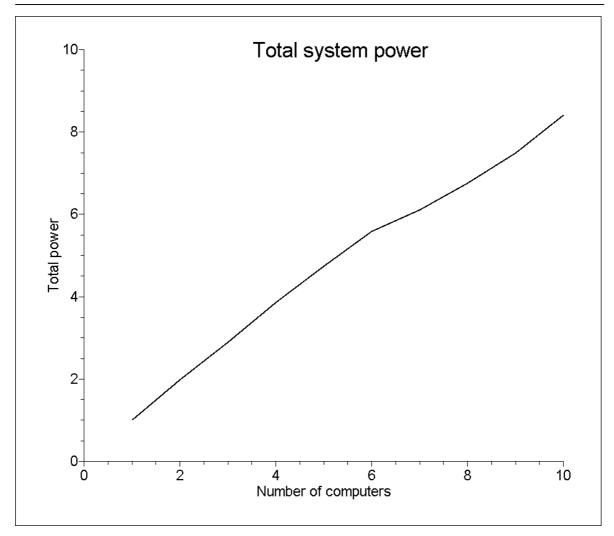

|     | Distributed system efficiency                     |  |

|     | Simulation procedure                              |  |

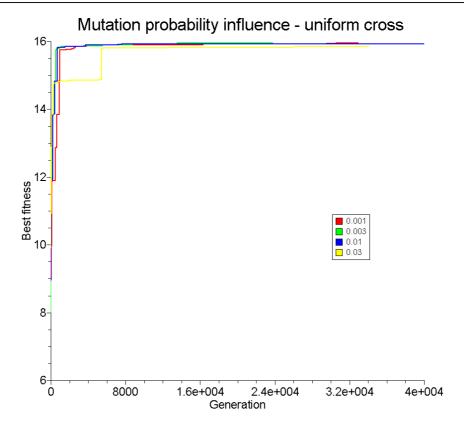

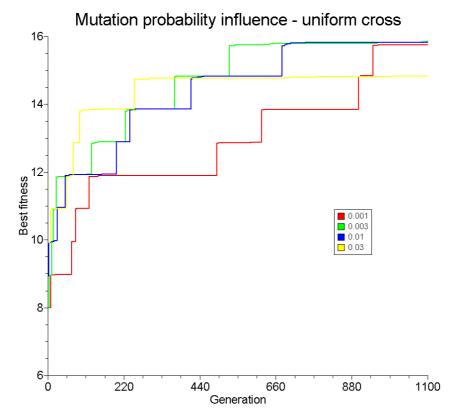

|     | Crossover operators comparison                    |  |

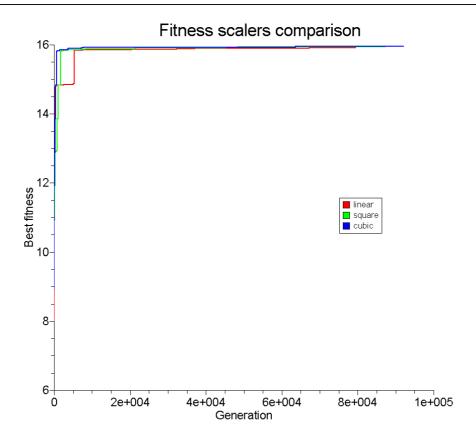

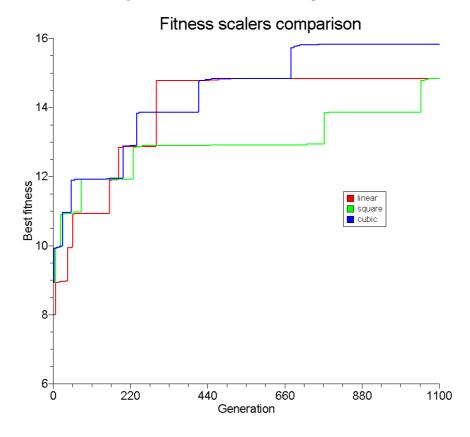

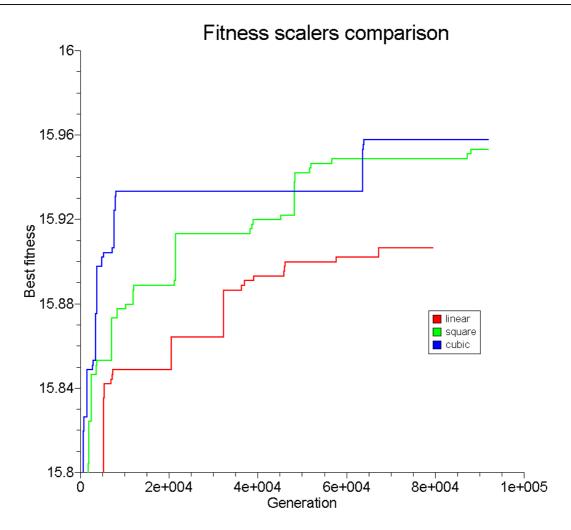

|     | Fitness scalers comparison                        |  |

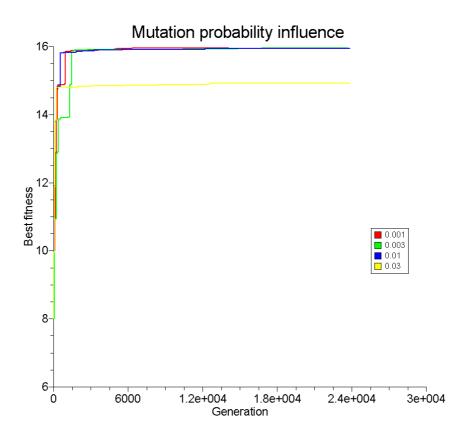

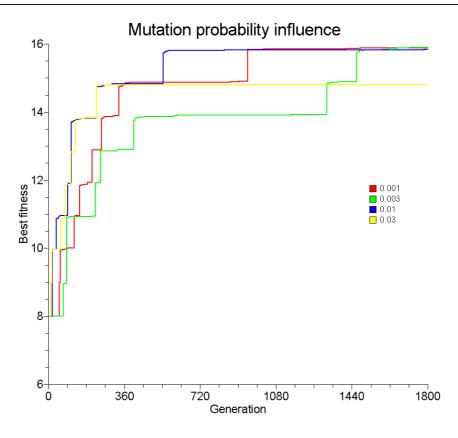

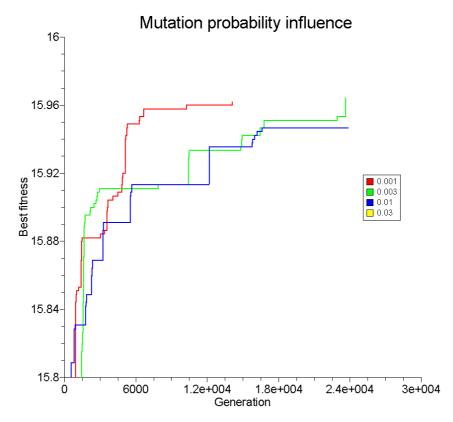

|     | Mutation probability                              |  |

|     | Length of the segment                             |  |

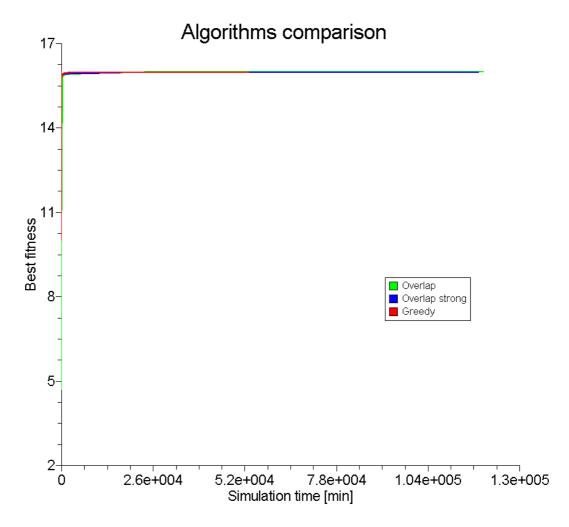

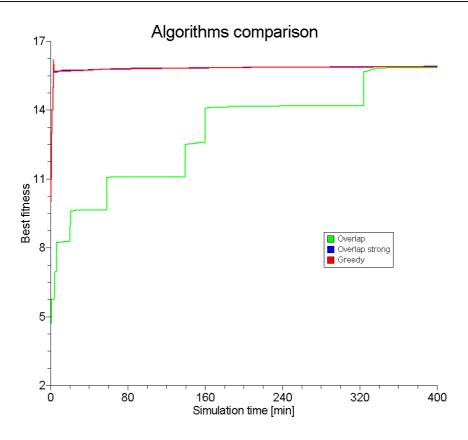

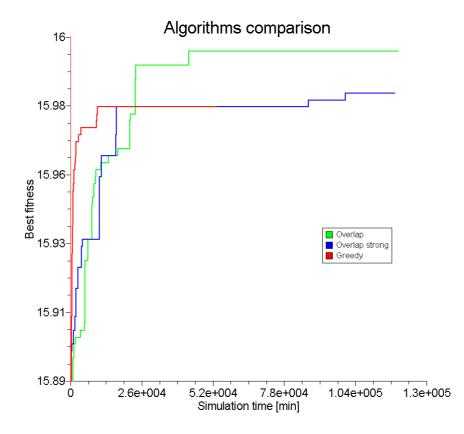

|     | Algorithms comparison (final simulation)          |  |

|     | Summary                                           |  |

| 6.  | SUMMARY AND CONCLUSIONS                           |  |

| REF | FERENCES                                          |  |

| A.  | APPENDIX A                                        |  |

| A   | .1. System Requirements                           |  |

| A   | .2. System Installation                           |  |

| A   | .3. USING THE SYSTEM                              |  |

|     | A.3.1. Genetic Manager                            |  |

|     | A.3.2. Genetic Node                               |  |

|     | A.3.3. Genetic Panel                              |  |

| A.  | .4. LOG FILES, SNAPSHOT FILES AND SYSTEM RESUMING |  |

| A   | .5. System Configuration                          |  |

| A   | .6. EXTENDING THE SYSTEM CAPABILITIES             |  |

| A   | .7. System Tools                                  |  |

|     | Logconverter                                      |  |

|     | Chrominfo                                         |  |

| A   | .8. ARCHITECTURE AND REFERENCE FILES              |  |

|     | Architecture File                                 |  |

|     | Reference File                                    |  |

| В.  | APPENDIX B                                        |  |

| C.  | APPENDIX C                                        |  |

# **1. Introduction**

The programmable circuits are becoming more and more important in contemporary electronic applications. Application Specific Integrated Circuits (ASICs) usage is justified only in high-volume projects. In most of the other tasks programmable circuits of many kinds are satisfactory and cost-effective solution. Their possibility of changing the configuration by the user is a great advantage and results in circuit flexibility, but can also become a curse when the device is placed in the high radiation environment. The device configuration can be changed by the radiation particle and result in functional failure. Chapter 2 describes mechanisms of radiation-matter interaction, radiation effects mitigation techniques, the types of programmable circuits and potential effect of radiation on those circuits.

One of the techniques, that can improve circuit reliability, is a formulation of special faulttolerant configuration, which despite some changes in its contents retains the functionality of the circuit. However, there are no widely available tools for the design of such configurations. Possibly the genetic algorithms can be used for that purpose. Chapter 3 explains the idea of genetic algorithms and presents the details of potential evolution application.

The simulation of the programmable circuit requires big amount of computational power, which is not easily accessible. This problem can be solved by the usage of distributed system, which will distribute tasks to many ordinary computers, thus increasing the available computational power. Chapter 4 describes the structure and functioning of the developed system.

Chapter 5 presents the results of simulations performed using the distributed system.

Chapter 6 contains conclusions drawn from the simulation results and summary of the thesis achievements.

## 1.1. Project Goals

The goal of the project is to design the distributed system for the circuit design using the genetic algorithms. The system should give access to the computational power enough for genetic simulations with no additional costs and at reasonable resources usage. Another goal is to verify the hypothesis that the genetic algorithms can be used effectively to improve the fault-tolerance of the programmable circuits by the design of special device configuration.

# 2. Impact of Radiation on Programmable Circuits

### 2.1. Radiation and Matter Interaction

There are several types of radiation, where different particles of different energies act. The quantum mechanics laws and theories description is far beyond the topic of this thesis, but at least brief explanation of terms used later throughout the chapter is essential. Nowadays, particles are thought to consist of **quarks** (which come in 6 flavours: up and down, charm and strange, top and bottom) and **leptons**. Quarks cannot be isolated; they are confined in particles called **hadrons** and held together by **gluons**. Furthermore, hadrons are divided into **mesons** (made of quark anti-quark pair) and **baryons** (made of three quarks). Hadrons interact via *strong interaction* and leptons via *photons*. The particles, which before 1970s were thought to be basic ones like proton, neutron and electron are accounted to the following groups: proton and neutron are baryons, electron is a lepton. Proton is build up from two up and one down quark and neutron is build up from one up and two down quarks. For full list of quantum particles, their properties and interactions between them please refer to [1].

Generally radiation interactions can be divided into two groups: ionising and non-ionising. Charged hadrons and leptons, heavy ions and photons are ionising particles, as they can ionise an atom. Neutrons and neutral hadrons cannot ionise atom directly, therefore are considered as non-ionising. However, neutrons can indirectly ionise atoms through the nuclear reactions. High-energy neutrons can excite an atom, which then emits gamma or x-ray radiation (photons with high energy). In the particle accelerator environment, which is the potential destination of the fault-tolerant programmable device, the presence of neutrons, electrons and gamma radiation is the basic danger.

### 2.2. Radiation Effects in Silicon

Under normal conditions radiation effects are not of a big concern. However, even at ground level, some space radiation particles can hit sensitive elements and cause failure of the system (in huge memory systems especially). They start to count seriously or become even critical when it comes to some special applications like space, military, avionics, nuclear power plants, High Energy Physics (HEP). Nowadays silicon integrated circuits are the most popular ones. They provide good speed, are cheap in production, but due to small elements size (for example gates of the transistors) and high packing density of the elements they are sensitive to radiation effects. Of course, one could argue that vacuum tubes are immune to radiation, but requirements like: circuit complexity, weight of the circuit, limited power consumption, mechanical resistance cannot be met by vacuum tube circuitry. In next few sections main radiation induced effects that occur in silicon circuits are presented.

### 2.2.1. Cumulative Effects

Cumulative effects alter semiconductor devices permanently. There are two main mechanisms accounted to the cumulative effects:

- Displacement damage

- Ionisation damage

Displacement damage occurs when incident quanta of sufficient energy hits semiconductor material, transfers momentum to the material atom, which in turn changes its place in the lattice. Such lattice defects have influence in the properties of the semiconductor material. They create so-called mid-gap states, which can result in generation of dark current (when electron from valence band goes to the conduction band via mid-gap state) in reverse-biased pn-junctions (shot noise), or recombination of the electrons from the conduction band with holes from valence band in forward-biased pn-junctions (reduction of signal or gain). When such mid-gap state is situated close to the edge of one of the bands, it can trap charge and release it after some time. Devices sensitive to this type of damage are bipolar transistors, optocouplers, and optical detectors.

Displacement damage does not depend on the total absorbed energy, but on the nonionising energy loss (NIEL), which refers to the mass and energy of the incident quanta. So it is important to take into account what type and energy of radiation particles is. The table 2.1. shows a comparison of relative displacement damage for different types of radiation [2]:

| Particle           | Proton | Proton | Neutron | Electron | Electron |

|--------------------|--------|--------|---------|----------|----------|

| Energy             | 1 GeV  | 50 MeV | 1 MeV   | 1 MeV    | 1 GeV    |

| Relative<br>damage | 1      | 2      | 2       | 0.01     | 0.1      |

| damage             |        |        |         |          |          |

Table 2.1. Comparison of relative displacement damage for different types of radiation

Ionisation damage occurs due to liberation of charge carriers from insulating layers (for example  $SiO_2$  used widely in silicon circuits for insulation) by ionisation mechanism. These free carriers drift or diffuse to other layers, where they can be trapped and contribute to parasitic fields. Freed electrons are much more mobile than holes, thus the latter are more probable to be trapped. Holes trapped in oxide layer contribute to positive charge build-up; on the other hand holes trapped at the silicon-oxide interface may result in electron trapping. For example, in NMOS transistor, holes produced by irradiation in the gate oxide cumulate in the oxide and build up positive charge. Therefore, threshold voltage decreases. However, this is true only at low radiation level, at higher level the threshold voltage increases and can even pass pre-radiation value. This is effect of formation of negatively charged acceptor interface traps. The change in PMOS transistor is smaller than in NMOS transistor, but positive charge trapped in the gate and lateral oxide decrease the threshold voltage. Such changes of the device characteristics can severely affect functioning of analogue circuits, because operation points change, but also of digital circuits, because switching times are affected.

Ionisation damages are independent on the type of radiation, but rather on the total absorbed ionising energy (Total Ionising Dose – TID). Typically the ionisation mechanism is the main absorption mechanism (for gamma radiation, hadrons, electrons and ions), therefore TID is usually expressed in terms of total energy absorbed per unit volume (1 rad = 100 erg/g or 1 Gray = 100 rads). The same TID causes ionisation damages of different scale in different materials; therefore, beside TID also absorbent material has to be stated.

### 2.2.2. Single Event Effects

Single Event Effects (SEEs) are result of hitting sensitive circuit elements by a single energetic radiation particle. Here we have to move to a statistical domain, since we cannot say exactly when such effect occurs, but we can just estimate probability of such event. SEE can be divided into permanent effects and transient effect. Permanent effects are those, which permanently change the structure of the device, so called "hard errors" for example Single Event LatchUp (SEL) in CMOS ICs, which turns on parasitic transistors in the circuits what destroys power lines if power is not turned off fast enough. Usually manufacturers care about latch up that can occur due to improper powering sequence, but do not take into account effects caused by radiation. Permanent effects similar to SEL occur also in power MOSFETs (Single Event Gate Rupture) and BJTs and power diodes (Single Event Burnout).

Transient effects affect functioning of the devices only temporarily, therefore, they have biggest impact on digital circuitry, and such effects in analogue circuits can even pass unnoticed. Examples of transient SEEs are Single Event Upsets (SEUs), which change contents of the memory and Single Event Transients (SETs) that are transient changes of the signals on the lines. When SEU changes bit in the register responsible for the functioning of the whole device, it can be called Single Event Functional Interrupt (SEFI).

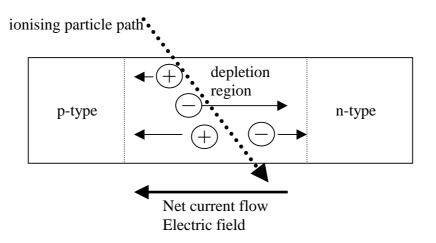

The single high-energy ionising particle can leave behind an ionised path of electron-hole pairs. When carriers are liberated in the depletion region electric field puts them in systematic motion and current spike occurs. Figure 2.1. illustrates the phenomenon.

Figure 2.1. Mechanism of charge deposition in depletion layer by high energy ionising particle

But the interaction of the ionising particle does not end just on the surface of the silicon device. It goes further and can deposit lot of charge in the bulk of device, which when collected can contribute to even higher current flow. This phenomenon is so called funnelling.

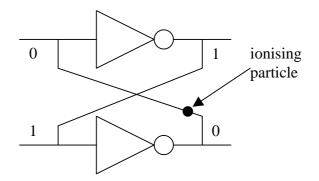

Current spike can produce flipped state on signal line, we have SET – a small glitch on the line, which can result in wrong output. But if such glitch occurs in memory cell, it can change its contents.

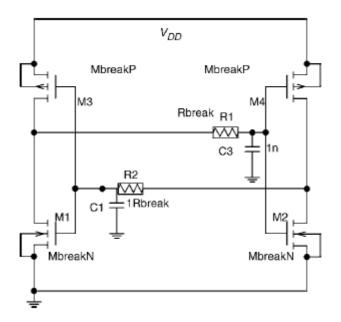

Figure 2.2. Bit-flip mechanism in Static RAM cell

Figure 2.2. presents SRAM cell or just a latch affected by ionising particle. If such particle changes state on any of the line (here we suppose it changes state from 0 to 1), the contents of the cell will be changed. In very sensitive devices, such single particle hit can even cause Multiple Bit Upset (MBU). SEUs are so called "soft errors", they do not impair the physical structure of the device, therefore, can be removed by reprogramming of the device. The rate at which SEUs occur depends strongly on the type of particles (type of radiation), energy of the radiation particles, device sensitivity and Linear Energy Transfer (LET). Device sensitivity, in turn, depends on the Sensitive Volume (SV) because not all elements of the device are sensitive to glitches on the lines and on the critical energy ( $E_{crit}$ ) – energy needed to change a state of the line. LET is the energy that can be transferred by given particle to the matter penetrated by the radiation on certain distance and. LET is defined in (2.1).

$$LET = \frac{dE}{dx}$$

(2.1)

For example heavy ions are high LET particles and hadrons are low LET particles. The probability of SEE is very hard to estimate, because not only heavy ions can deposit energy bigger than critical energy. Hadrons that are not able to deposit sufficient energy in sensitive volume can by nuclear interaction produce heavy ions and thus deposit energy bigger than  $E_{crit}$ .

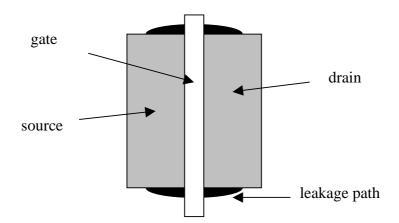

### 2.3. Mitigation Techniques

Mitigation in case of effects connected with cumulative effects can be done on the physical structure level. As we can imagine, the number of carriers liberated in the insulation layer depends strongly on the thickness of this layer. Therefore, in order to minimise the effect of ionisation damage or displacement damage, we have to reduce the thickness of the insulating layer, what in practice means, use the device produced in smaller gate length technology. Not only the thickness of the gate oxide is the problem, but also oxide insulating two adjacent transistors in the IC - field oxide (which is usually much thicker than gate oxide and unfortunately does not scale down with gate length) has to be taken into account. Trapping of the charges at the oxide-silicon interface can lead to leakage current (holes trapped in the field oxide-silicon interface can create inversion layer) between two transistors what produces increased power consumption and can lead to IC malfunction. Thick oxide near source and drain edges can be a problem. Parasitic transistors can be created there, because whole device is covered with thick oxide layer (except the area under the gate). The figure below explains the problem.

Figure 2.3. Parasitic leakage paths in MOS transistor

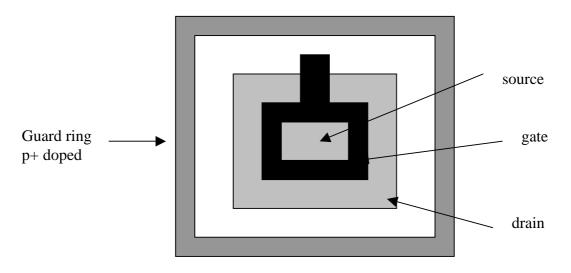

The solution to those two problems is device guarding. This is technology-hardening method. The idea is explained in the figure 2.4.

Figure 2.4. Guard ring and gate surrounding the source

The gate totally encloses source, so parasitic transistors do not create because gate oxide is thin enough to restrict or even eliminate cumulative radiation effects. Heavily doped p+ guard ring cuts the leakage current between two adjacent devices, because holes trapped at the oxide-silicon interface will not be able to create inversion layer.

Unfortunately every solution has its drawbacks. This solution increases size of the IC elements, what in turn results in decreased circuit speed, worsens packing density and increases power consumption.

It is also worth mentioning, that cumulative effects of radiation can be removed by device annealing.

The technology goes forward very quickly, the devices are scaled down what reduces consumed power, increases switching speed and increases number of devices per area unit. When scaling down  $V_{DD}$  is decreased and capacitance of the individual devices decreases, thus critical energy is also smaller. But we have to remember, that sensitive volume also decreases due to smaller feature size. In DRAM cells the cell area scaling seems more important than decrease of capacitance, and therefore DRAM sensitivity decreases when scaling down. For SRAM answer is not so clear, it seems that both phenomena cancel each other [4], but experimental results show, that error rates increase with scaling [5].

There are different ways to eliminate or limit SEEs. One of the approaches is to change physical structure of the device to make SEE less probable. It is so called "hardware hardening". One of the ideas is Dual Interlocked CEll (DICE) structure [6], which adds

some redundancy to the circuit. The latch in this structure requires voltage change on two nodes in order to change the information stored in a cell. But technology is successively scaled down and it becomes probable, that one incoming ion can produce MBU and cause bit flip in the DICE cell. The Triple Interlocked CEll (TICE) is under investigation and should be much more immune to SEUs. Other circuit level idea of hardening the device is resistor-decoupling technique, where resistor is put in series with each inverter gate. The resistor, together with inverter gate capacitance, forms RC low-pass filtering circuit. This filtering circuit can filter out high frequency components and thus eliminate current spike at signal line. But again scaling down of a feature size becomes a problem. With smaller gate length, the capacitance of the gate decreases and to keep filtering circuit cut-off frequency at desired level, we have to increase the resistance. With large resistance values (order of M $\Omega$  in technology 0.25 µm [6]) the technological aspect starts to play significant role. Resistors that can provide such resistance are strongly thermally dependent and can change cell characteristics considerably over operating temperature interval. The solution to this issue is additional capacitor inserted in parallel to the signal line. This leads to reduction of the required resistance.

Figure 2.5. RC radiation hardened SRAM memory cell [6]

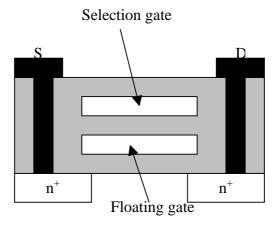

Above presented methods are used for "hardware hardening" of SRAM cells, so volatile memory cells. In case of non-volatile memories, like EPROMS, EEPROMS and FLASH memories other methods have to be used. Usually such memories are built using floating gates. Floating gate is similar to the normal transistor, but it has two gates (selection gate and floating gate). The structure is shown in figure 2.6.

Figure 2.6. Floating gate transistor structure

The floating gate is isolated from the substrate with thin tunnel oxide ( $t_{ox} < 100$  Å). When high voltage is applied (about 20 V) between Source and Selection gate - Drain, high electric field is created, which causes avalanche injection of the electrons to the floating gate, where they get trapped. Accumulation of the charge in the floating gate changes the threshold voltage of the device towards the higher voltages. This process is selflimiting, the charge build-up in the floating gate effectively lowers the electric field and stops avalanche injection. The state of the device (stored information) is checked using Selection Gate. The low voltage (just enough to overcome the threshold voltage of nonprogrammed device) is applied to the Selection Gate. If the floating gate does not hold accumulated charge - the inversion layer is created and current can flow between source and drain (device stores "0"), but if it holds some charge, inversion layer cannot be formed and there is no conduction path between source and drain (device stores "1"). Silicon dioxide isolates floating gate from any conducting parts of the circuit and once programmed, device can hold information for decades, because leakage of the charge is very, very small. In EPROM data can be erased by strong UV irradiation (what generates some electron-hole pairs) in the oxide and allows charge to leak from the floating gate. UV erasure is very slow; therefore EEPROM is in wider use. In EEPROM tunnelling mechanism is reversible by high negative voltage.

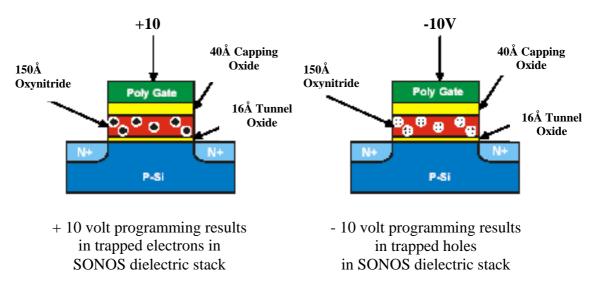

Memories built using floating gates differ from the volatile memories mentioned earlier and have different radiation sensitivity. Experimental data proves that TID effects are main reasons of data loss in floating gate devices [7]. The ionising damage puts some variation on threshold voltage of the devices, moreover, it can damage the tunnelling oxide and cause charge leakage. But not all experimental results can be justified by cumulative radiation effects. Heavy ion can discharge the floating gate devices [8]. The solution to this problem is the Silicon-Oxide-Nitride-Oxide-Silicon (SONOS) device. The technology has been developed by Northrop Grumman Corporation (NGC), which is involved in space applications of non-volatile memories for over 30 years. The structure of such device is shown in the figure 2.7.

#### Figure 2.7. SONOS transistor stack [8]

These are stacked transistors. First there is 15 Å of thermal oxide, than 150 Å of silicon nitride, 40 Å of blocking oxide and phosphorous-doped polysilicon gate. Positive voltage of 10 V applied to the gate results in electrons trapped in nitride layer, negative voltage results in holes accumulation. The charge is stored in traps in silicon nitride layer, therefore it cannot be removed as easy as in case of conducting polysilicon floating gate. The retention of the data depends on the width of programming pulse, but is between 10 to 100 years! The number of reprogramming cycles is estimated to be 100,000 times.

We have to keep in mind, that while such methods (on the hardware level) are very effective and do not require changes on the higher levels, they are also very expensive. The radiation-hardened devices are not widely used, they are suitable only for certain applications, therefore are produced in small series, what increases the price. Moreover research and development of such circuits requires many expensive tests and experiments

may require change of the technology in the silicon foundry. Sometimes, when we deal with environment in which radiation effects are not so severe and often, it is better to use commercial ICs, but use radiation hardening on the system design level ("software hardening").

Obvious hardening method implemented at system design stage is data duplication. Of course, we can use two separate places to store the same data; everything is fine until no data difference occurs. When data from one storage is different than from the second one, we have to decide somehow, which is the true value. We have implement at least some error detecting coding scheme. This approach has its drawbacks: double memory needed to store data, slow memory access due to coding/decoding and double copying. But if we have to implement at least error detecting coding, maybe we could sacrifice some speed, but use only one storage place to store data with Error Detection And Correction (EDAC).

Coding schemes which allow error detection or detection and correction need some redundancy. We have to add some bits to the information to facilitate detection and correction. Some memory ICs have even dedicated EDAC circuitry, but due to costs this is not true in commercial ones. In such a case, we have to implement EDAC entirely in software. Of course the problem is that usually code and data is stored in SRAM and therefore is sensitive to SEEs. When error occurs in data, this is not a problem, the EDAC would correct the single error, but error in code can lead to IC malfunction. The code memory segment can be also protected with some redundant bits, but if error occurs in the instruction that is going to be executed, the unpredictable behaviour can be the result. Coming back to the protecting coding schemes. There are two type of coding schemes: systematic (separable) and non-systematic (non-separable). Separable codes keep protected data intact, but add some check bits. Non-separable codes mix check bits with data bits. In our case it seems reasonable to use systematic coding to keep data in memory as is, but keep some additional data to be able to detect and correct errors.

One of the most popular and simple coding scheme is parity checking. This code adds one bit to the information and is able to detect odd number of errors, but cannot correct any errors. Usually even parity is used. It means that extra bit keeps number of "1"s in the protected information always even. Suppose, the 8-bit information is protected. Table 2.2. presents the idea of even parity checking.

|          | D:4 7 | D:4 ( | D:4 5 | D:4 4 | D:4 2 | D:4 0 | D:4 1 | <b>D</b> :4 0 | No of | Parity | Check  |

|----------|-------|-------|-------|-------|-------|-------|-------|---------------|-------|--------|--------|

|          | Bit 7 | Bit 6 | BII 2 | DIL 4 | ын э  | BIL 2 | BII I | DIUU          | "1"s  | bit    | result |

| No error | 0     | 1     | 1     | 0     | 1     | 1     | 0     | 1             | 5     | 1      | OK     |

| 1 error  | 0     | 1     | 1     | 1     | 1     | 1     | 0     | 1             | 6     | 1      | Error  |

| 2 errors | 0     | 1     | 1     | 1     | 1     | 1     | 1     | 1             | 7     | 1      | OK     |

| 3 errors | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1             | 8     | 1      | Error  |

Table 2.2. Even parity checking can find only odd number of errors

As we can see parity checking is not very suitable in case of SRAM protection against errors resulting from SEEs. It only detects errors, but cannot correct any, what could only help in case of doubled memory storage. Method can be modified to enable error correction. Data is stored in the memory usually in 8-bit addressable cells. Apart from one extra parity bit for each cell as horizontal protection, one cell is devoted to vertical protection. Table 2.3. presents 3 memory cells protected with 8 vertical and 3 horizontal parity bits and Table 2.4. same memory with single error.

| Address                | Bit | Horizontal |

|------------------------|-----|-----|-----|-----|-----|-----|-----|-----|------------|

|                        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | Parity bit |

| 0x0000                 | 1   | 0   | 0   | 1   | 1   | 1   | 0   | 0   | 0          |

| 0x0001                 | 1   | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 0          |

| 0x0002                 | 1   | 1   | 1   | 1   | 0   | 0   | 0   | 0   | 0          |

| Vertical<br>Parity Bit | 1   | 1   | 0   | 0   | 0   | 1   | 1   | 0   |            |

Table 2.3. Three memory cells protected with vertical and horizontal parity

Table 2.4. Three memory cells protected with vertical and horizontal parity with one error

| Adduces                | Bit | Horizontal |

|------------------------|-----|-----|-----|-----|-----|-----|-----|-----|------------|

| Address                | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | Parity bit |

| 0x0000                 | 1   | 0   | 0   | 1   | 1   | 1   | 0   | 0   | 0          |

| 0x0001                 | 1   | 0   | 1   | 1   | 1   | 0   | 1   | 0   | 0          |

| 0x0002                 | 1   | 1   | 1   | 1   | 0   | 0   | 0   | 0   | 0          |

| Vertical<br>Parity Bit | 1   | 1   | 0   | 0   | 0   | 1   | 1   | 0   |            |

Single error position can be precisely determined and corrected. More errors can be corrected, but only when no two errors occur simultaneously in the same row or column. In such a case, only odd number of errors can be detected in the row or column. It has to be kept in mind, that every protection method adds significant overhead to the read/write operations and needs some additional memory. In this case, every 8 bytes of protected memory require 10 bytes of storage, 1 byte for horizontal parity bits, 1 byte for vertical parity bits. Of course vertical parity byte does not have to be inserted after every 8 bytes of memory, it can be put more often or less often. This strongly depends on the probability of double errors in one row or column in smallest cross-protected area.

Another frequently used protection code is Hamming code. Is also based on additional parity bits, but it allows to correct single error or detect up to two errors, but not both simultaneously. The number of required additional bits is determined by "Hamming rule":

$$2^m \ge m + d + 1 \tag{2.2}$$

Where d is the number of data bits to protect and m is the number of parity bits. A code, which is constructed in such a way, that equality sign can be used in (2.2) is called a perfect code. Codes are denoted as (m+d, d) Hamming codes.

Suppose, the (7,4) Hamming code is constructed. There are 4 data bits and 3 parity (check) bits in this code, which can indicate 7 positions of an error, position 000 indicates no error. In such a code parity bits are also protected. Table 2.5. shows positions of errors and corresponding parity bits values.

| Position | Bit 2 | Bit 1 | Bit 0 |

|----------|-------|-------|-------|

| 1        | 0     | 0     | 1     |

| 2        | 0     | 1     | 0     |

| 3        | 0     | 1     | 1     |

| 4        | 1     | 0     | 0     |

| 5        | 1     | 0     | 1     |

| 6        | 1     | 1     | 0     |

| 7        | 1     | 1     | 1     |

Table 2.5. (7,4) Perfect Hamming code parity bits values

Bit 0 is responsible for parity check on positions 1, 3, 5, 7. Bit 1 on positions 2, 3, 6, 7. Bit 2 on positions 4, 5, 6, 7. The rule is that code should be constructed in such a way, that

no parity bit checks the other parity bit. This can be achieved by placing parity bits on positions 1, 2, 4, since these positions contain only one "1" in binary representation and are checked only once. Parity bits are determined exactly in the same way, as in even parity coding, for example 1 Parity bit is 0 since bits on positions 3, 5, 7 are 1, 0, 1 (two "1"s in total). As an example consider the following data: 1011. The resulting Hamming code looks as in Table 2.6.

| Position | 1        | 2        | 3      | 4        | 5      | 6      | 7      |

|----------|----------|----------|--------|----------|--------|--------|--------|

| Function | Parity 0 | Parity 1 | Data 3 | Parity 2 | Data 2 | Data 1 | Data 0 |

|          | 0        | 1        | 1      | 0        | 0      | 1      | 1      |

Table 2.6. Hamming code for 1011 data

Decoding is a matrix multiplication of matrix containing possible combinations of parity bits and received data. Modulo 2 arithmetic has to be used to calculate the multiplication. In this case:

$$\begin{bmatrix} 0 & 0 & 0 & 1 & 1 & 1 & 1 \\ 0 & 1 & 1 & 0 & 0 & 1 & 1 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 \end{bmatrix} \begin{bmatrix} 0 \\ 1 \\ 0 \\ 0 \\ 1 \\ 1 \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ 0 \end{bmatrix}$$

(2.2)

What indicates that there is no error (error position 000). The erroneous data 0010011 would give:

$$\begin{bmatrix} 0 & 0 & 0 & 1 & 1 & 1 & 1 \\ 0 & 1 & 1 & 0 & 0 & 1 & 1 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 \\ 1 & 1 & 1 & 1 & 1 \end{bmatrix} \begin{bmatrix} 0 \\ 0 \\ 1 \\ 0 \\ 1 \\ 1 & 1 \end{bmatrix}$$

(2.3)

what indicates error on position 010 = 2. The mechanism of error detection and correction by Hamming code is based on Hamming distance. Hamming distance is the number of bits at which two code words are different and Hamming rule ensures that that distance between any two valid code words is at least 3. Therefore, to change from one valid code word, to another code word, at least 3 bits have to change. When only one bit changes, it is possible to decide which was the correct valid code word and correct the error, because this is the only one with Hamming distance of 1 from the code word read with error. When two bits change, it is only possible to detect that double error occurred, because read code word is not valid. Unfortunately error cannot be corrected since it is close (Hamming distance = 1) to another valid code word. That is why perfect Hamming code is able to correct single error and detect double error, but cannot do both functions simultaneously. Of course, code with bigger Hamming distance between any two valid code words can be selected. For example code (7,3) is able to correct single error and detect double error simultaneously (minimum Hamming distance is 4). One could say that Hamming code is non-separable code and is hard to implement in hardware. But we can make it separable by moving parity bits to the end of the data. Implementation is also simple. XORing appropriate bits can do the coding. For example bits on positions 3, 5, 7 in the above considerations were 1, 0, 1. Therefore Parity bit 0 is:

$$p_0 = b_3 \oplus b_5 \oplus b_7 = 1 \oplus 0 \oplus 1 = 0 \tag{2.4}$$

Decoding is also straightforward. First the error position has to be determined. For example for received data r = [0010011]:

$$e_{0} = r_{1} \oplus r_{3} \oplus r_{5} \oplus r_{7} = 0 \oplus 1 \oplus 0 \oplus 1 = 0$$

$$e_{1} = r_{2} \oplus r_{3} \oplus r_{6} \oplus r_{7} = 0 \oplus 1 \oplus 1 \oplus 1 = 1$$

$$e_{2} = r_{4} \oplus r_{5} \oplus r_{6} \oplus r_{7} = 0 \oplus 0 \oplus 1 \oplus 1 = 0$$

(2.5)

If the position of error is different than 000, the bit has to be flipped.

There are other simple and more sophisticated coding schemes [9], which could be employed for memory protection against SEE induced errors, but there is no point in describing them here.

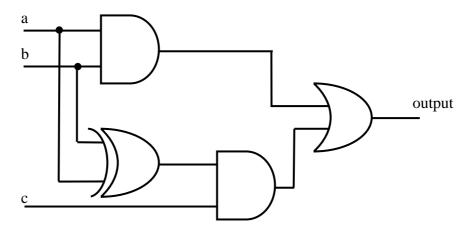

Until now, the memory protection techniques were mentioned, but systems as a whole are also subject to SEEs. For example SETs can change output of a device for a short time. It is not important, whether it is combinatorial circuit or sequential circuit; it produces bad output for a while. This can lead to malfunction of other connected systems. One of the techniques, which alleviate this problem, is voting circuit. This technique has been used for many years in electronic devices working in space. The idea is simple. There are three modules, which perform the same function and are subject to SEEs. Their outputs are connected to the inputs of voting circuit. If two of them have the same output and the third has different or all of the three have the same outputs, the output of the voting circuit is set to the value that is present on the majority of inputs of the voting circuit. The figure 2.8. presents example of voting circuit implementation.

Figure 2.8. Voting circuit implementation

When implemented in programmable circuit, which stores its configuration in memory insensitive to radiation or built from the discrete elements the voting circuit is only a subject to SET. However, it is very simple and small and probability of SET is usually small. Of course, when voting circuit is implemented in the programmable circuit, which stores its configuration in memory sensitive to radiation, voting circuit also becomes a subject to SEUs.

### 2.4. Programmable Circuits

Mass-produced Integrated Circuits (ICs) are usually relatively cheap, fast and widely available, moreover the selection of IC types and manufacturers is so big, that many projects can be realised using only "stock" ICs. But in some cases an Application Specific Integrated Circuit (ASIC) is needed because of project requirements, which can be for example device size, speed or power consumption. However, because of low quantity production ASIC manufacture process is usually long and expensive. Therefore, many prototypes and even many final products are built using programmable circuits. Most of the combinatorial or sequential circuits can be realised using these Field-Programmable Devices (FPDs). They are produced in large quantities, what decreases the unit cost, but are flexible and can be programmed to realise user defined functions, what in turn lowers the start-up cost and the financial risk of the project.

Taking into account the complexity of those circuits, they can be divided into three groups: Simple Programmable Logic Devices (SPLDs), Complex Programmable Logic Devices (CPLDs) and Field-Programmable Gate Arrays (FPGAs).

#### **SPLDs**

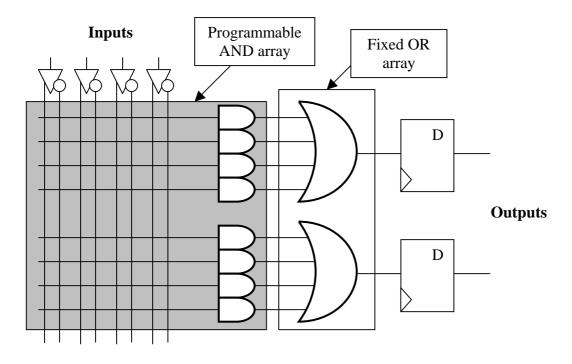

SPLDs are usually devices with programmable AND array followed by fixed or programmable OR array. Programmable Logic Array (PLA) devices have programmable AND and OR arrays, but this introduces significant propagation delays and the need for fast programmable circuits led to Programmable Array Logic (PAL) devices developed by Advanced Micro Devices. In PALs only AND array can be programmed and OR array is fixed. Architectures of programmable devices vary from vendor to vendor what is reflected in vendor-specific device names, like Generic Array Logic (GAL – Lattice Semiconductors trademark) which is a variation of PAL architecture with some additional features. GAL device is described later as an example. Array outputs can be registered to facilitate sequential circuits functions. Figure 2.9. presents the simplified structure of PAL device. In the figure, the short notation for AND matrix connections is used. Horizontal lines do not represent a single connection to the AND gate, but connections to all vertical lines that cross them. Moreover, usually there are more than 4 inputs and 2 outputs. Different configurations of PAL devices are available. The configuration of the device can be identified by the device name. For example 16R8

indicates maximum of 16 inputs and maximum of 8 outputs. The letter "R" means that the outputs are registered, other commonly used letter "V" means "versatile" and indicates that the outputs can be configured in various ways.

Figure 2.9. Simplified PAL structure

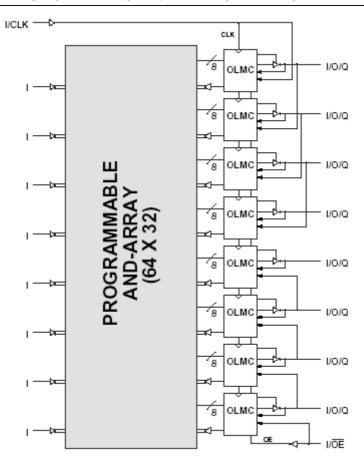

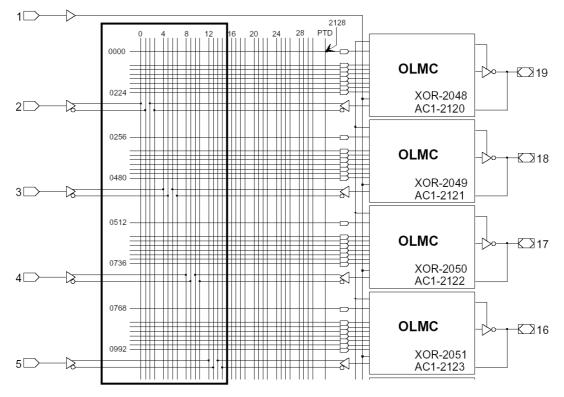

Good example of PAL device is GAL16V8 from Lattice Semiconductors, which is used in simulations throughout this thesis. Its functional block diagram is shown in the figure 2.10.

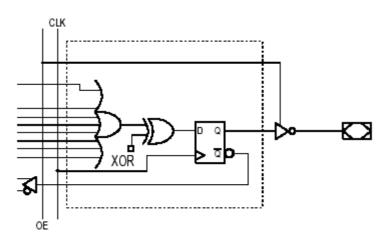

The Output Logic Macro Cell (OLMC) is the generic feature of this device, making it different from the standard PAL structure. The OLMCs can be configured with 2 global and 16 individual configuration bits into three operation modes: simple, complex and registered. The figure 2.11. shows internal OLMC structure in registered configuration for registered mode. In this mode all macrocells share common clock (CLK) and output enable (OE) control pins, any of the macrocells can be configured as registered output or input/output. XOR controls the polarity of the output. The output can be fed back to the AND matrix. In other modes register or feedback can be disabled. The configuration of the device is kept in the EEPROM memory, thus it is immune to SEUs. For further information, please refer to [10].

Figure 2.10. GAL16V8 Functional block diagram [10]

Figure 2.11. OLMC structure in registered configuration for registered mode [10]

#### **CPLDs**

CPLDs are the next step in programmable circuits evolution. SPLDs capacity cannot be easily increased because the programmable matrices take too much silicon area when number of inputs and outputs is increased. Therefore, CPLDs are based on many SPLD-like blocks connected together to increase the programmable circuit resources.

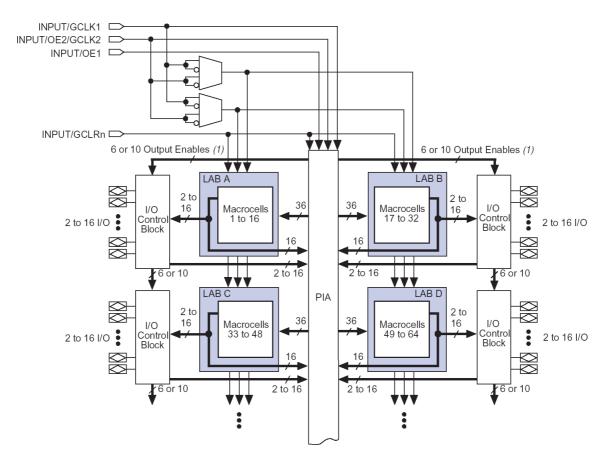

The good example of CPLD is Altera MAX 3000 family. These devices contain from 32 to 512 macrocells. The device structure is shown in the figure 2.12.

Figure 2.12. Altera MAX3000A device block diagram [11]

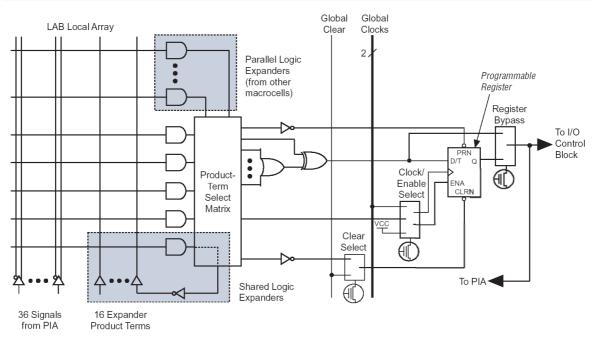

16 macrocells form a Logic Array Block (LAB). LABs are interconnected via Programmable Interconnect Array (PIA). PIA is fed by I/O pins, input pins and macrocells. The macrocell structure is shown in the figure 2.13. Each macrocell is similar to the PAL device. The Product Term Select Matrix (AND matrix) is programmable and product terms are directed to the OR and XOR gate. This part realises combinatorial logic functions. Register at the output of the macrocell can be used for sequential circuits. Two types of logic expanders are present in the macrocells. The Shared Logic Expanders enable inverted product terms to be fed back into the logic array. The Parallel Logic Expanders enable product terms from adjacent macrocell to be borrowed.

Figure 2.13. Altera MAX 3000A macrocell structure [11]

The configuration of the device is kept in EEPROM memory and the device is In-System Programmable (ISP), what means, that it does not have to be programmed in separate programming device, but its configuration can be changed in the target system. For further information, please refer to [11].

The Altera MAX programmable logic devices family is only one of many available on the market. Each vendor uses different device architecture, therefore the device type and vendor must be selected carefully, with all project requirements in mind.

#### **FPGAs**

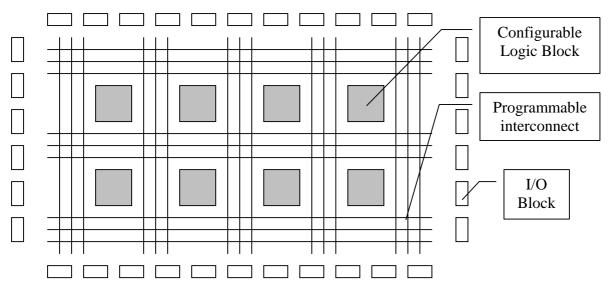

Because some projects require more resources (more gates or registers) than CPLDs offer, the next group has been developed. The FPGA structure is not an extension of the CPLD architecture, but employs different approach. There is no longer product term selection matrix, but the combinatorial functions are realised using Look-Up Tables (LUTs). The typical FPGA structure is shown in the figure 2.14.

The Programmable Logic Blocks (PLBs) are interconnected using Programmable Interconnect. I/O Blocks control the pin functions.

Figure 2.14. Typical FPGA structure[12]

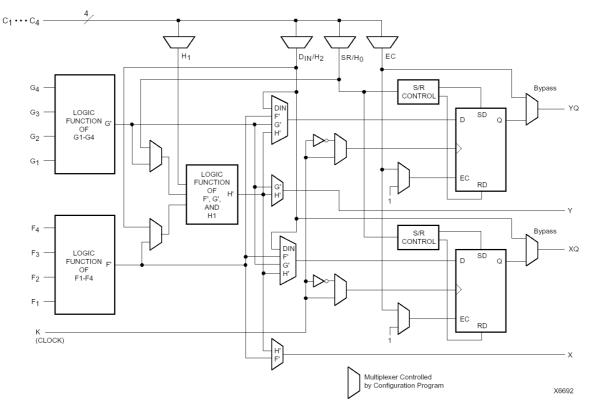

It is good to describe the details of architecture using some exemplary programmable logic device. The good example is Xilinx XC4000 FPGA family. The figure 2.15. shows the structure of Xilinx XC4000 Configurable Logic Block (CLB).

Figure 2.15. Block diagram of Xilinx XC4000 CLB [13]

The three logic function generators, built using LUTs, are provided. The G and F generators have 4 inputs, the third generator (H) has three inputs. The inputs of the H generator can be the outputs of G and F generators or inputs from outside the CLB. The sequential circuits are realised using two D flip-flops. The flip-flops can be fed by the logic function generators outputs or external signal. Moreover, combinatorial logic and the storage elements can be used independently, because there are separate, non registered outputs available (X, Y) for combinatorial logic. The LUTs used for logic function generators are simply the 16x1 bit SRAM memory areas. The inputs are address lines of the memory and the stored value is a function value. In this family of programmable logic devices, the function generators can be used also as high speed RAM, the single CLB can be configured as 16x1, 16x2 or 32x1 bit array. LUT usage in logic function generators makes the propagation time independent on the function implemented.

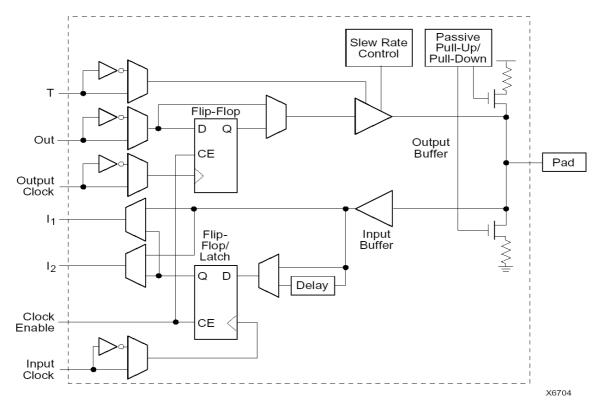

Figure 2.16. shows the I/O block structure.

Figure 2.16. I/O Block structure [13]

The I/O blocks are interfaces between external device package pins and the internal connections. Each pin has its dedicated I/O block. The  $I_1$  and  $I_2$  inputs can be connected

to the pad directly (via the buffer) or through the D flip-flop, which can also be configured as latch. The Out output can also be connected directly to the pad (via the buffer) or through the D flip-flop. The input and output storage elements have common Clock Enable signal (CE), but use different clock signals. The output signal can be inverted in the I/O Block. The output buffer can be configured in the high-impedance state (using T signal).

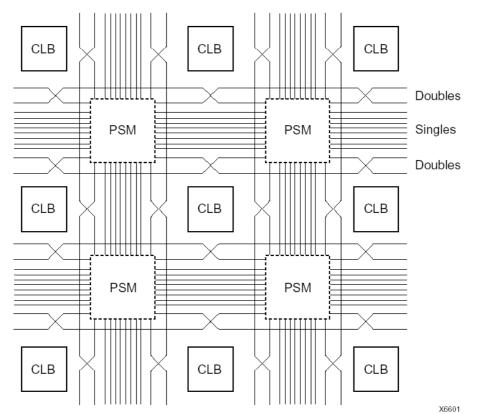

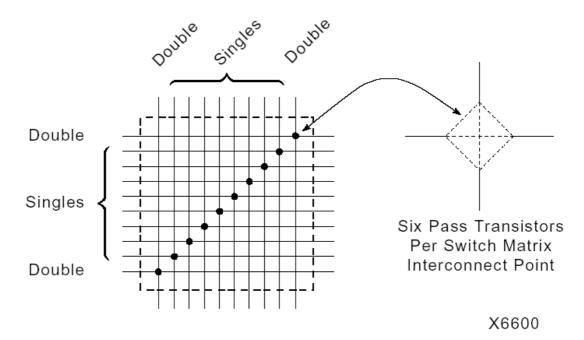

The last detail of Xilinx XC4000 family architecture that needs explanation is the programmable connection between CLBs. These devices use hierarchical wiring structure. Namely, each CLB is connected to the five types of interconnects: length-1 lines, length-2 lines, length-4 lines, length-8 lines (only in XC4000X) and long lines. This feature simplifies the routing procedure done by the design software and enables better device resources usage. The wire segments are placed horizontally and vertically around the CLB. The cross points of vertical and horizontal wiring lines are called Programmable Switch Matrices (PSMs). The figure 2.17. shows single and double-length lines in the device and figure 2.18. shows internal structure of PSM.

Figure 2.17. Single and double-length lines [13]

Figure 2.18. Programmable Switch Matrix

Additional wiring is placed in the outer device ring formed by I/O blocks routing.

The configuration of the Xilinx XC4000 family devices is stored in SRAM and therefore is a subject to SEUs. Xilinx XC4000s are mature products, there are much more powerful devices nowadays, but the family has been chosen as an example because of its relatively simple inner structure. For example Xilinx's Virtex-4 family of the FPGA devices belongs to the one of the most powerful on the market. The members of that family have many additional features beyond the programmable logic. These are: PowerPC 405 processor core available (PowerPC is an IBM trademark), an interface for user coprocessor, 622 Mb/s to 10 Gb/s serial transceivers, Digital Signal Processing slices (which can act as a simple DSP processors). The programmable logic is based on Advanced Silicon Modular Blocks (ASMBLs). For further information please refer to [14].

#### Radiation influence on the programmable circuits

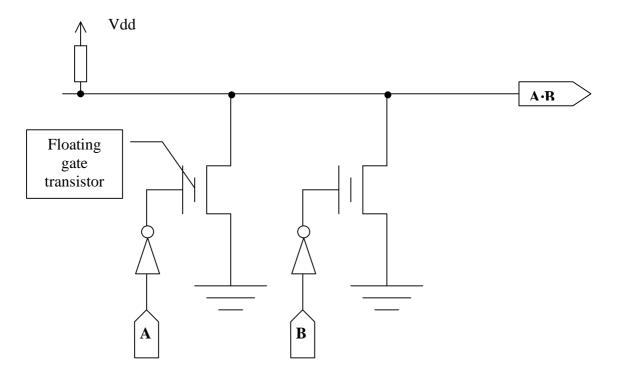

In order to describe the influence of the radiation on the programmable circuits, it is advisable to describe the user-programmable switch technologies. The programmable switches are the key elements that enable different device configuration options. EPROM or EEPROM based devices use structure presented in the figure 2.19.

Figure 2.19. EPROM programmable switches realising AND function

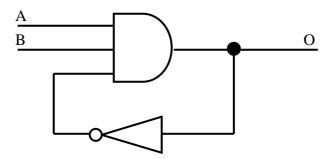

These switches are build using floating gates. When the gate is charged (stores "1") the input signal cannot change the state of product wire (the conducting path to ground cannot be formed). Therefore, only signals lines, where switch stores "0" contribute to the product. The arrangement shown above with inverters put on the inputs realises AND function if two floating gates are unprogrammed (store "0").

SRAM based switches are simply pass-transistors with gates controlled by appropriate SRAM bits. The pass transistors are used in PSM as shown in the figure 2.18.

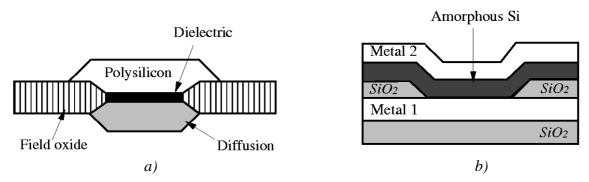

FPGA circuits employ also another programming technology – antifuse technology. This is one time programmable switch, which is build using CMOS antifuses. Antifuse is a device, that functions in an opposite way than the fuse does. It is composed of and insulating layer sandwiched between two conducting layers. Antifuse is initially non-conducting, because conducting layers are separated by the insulator. When current is passed through the antifuse (~5mA), the insulating layer melts and the conducting path is created. Figure 2.20. shows two commonly used antifuse technologies.

Figure 2.20. Antifuse technologies: a)ONO antifuse b) amorphous antifuse [15]

The Actel's antifuse uses Oxygene-Nitrogen-Oxygene (ONO) dielectric layer put between polysilicon and  $n^+$  diffusion layers. Quicklogic's antifuse employs amorphous silicon between two metallization layers.

Above considerations lead to the conclusion that the only switches that are subject to SEUs are SRAM based switches. Therefore SPLDs and CPLDs using EEPROM memory are only subject to SETs. FPGAs using SRAM for device configuration are a subject to SETs and SEUs. SEUs can affect interconnections between CLBs and LUTs as well. There are FPGAs using antifuse technology for interconnections programming, but this still does not alleviate problem of LUTs stored in SRAM. All devices are subject to cumulative radiation effects.

# 3. Application of Genetic Algorithms in Fault-Tolerant Circuit Design

As described in chapter 2 techniques mitigating the influence of radiation on the programmable circuits are implemented at different levels of circuit design process. The technique proposed below is implemented on the system design level. System is to be designed in a way, which minimises negative effects of bit flips in configuration data of programmable circuit. The ideal "radiation tolerant" configuration would provide proper device functioning with any of its bits flipped. Due to complexity of this task, only single error tolerance is assumed. Length of programmable circuits configurations depend on the type of the designed system and type of target device. Simplest configurations realizing simple combinatorial circuits in GALs have lengths of hundreds of bits. This gives enormous solution space, which cannot be searched in reasonable time using "check all" method. Search has to be directed somehow towards right solution. Genetic Algorithms (GAs) can be helpful in this case.

### 3.1. Genetic Algorithms

### 3.1.1. Idea of GAs

There are problems, where solution is contained in large search space. This is the case, when there are many parameters that have to be optimised simultaneously to find the right combination. Solution space size depends on the number of parameters and possible parameter values. Optimisation problems may be solved using analytical or numerical methods. However, former approach is applicable only to the class of problems, which can be described as analytical function. Usually real-life problems are complex and are difficult or impossible to describe analytically and can be solved only numerically, by searching in solution space. When the number of possible solutions is not too large, we can check all possible combinations and choose the best one. This approach is always successful, it always gives the best solution, or in other words global extremum of the function. But application of this algorithm is limited by the computational power of the computer used for program execution. Random searching could be employed, but this approach requires also much of CPU power, because the longer the algorithm runs, the better final solution we get. Moreover, the quality of the final solution depends on luck and does not guarantee that satisfying solution will ever be found. In cases of huge search space some Artificial Intelligence (AI) should be employed to direct search toward the places in the space with better solutions. Genetic Algorithms employ some sort of AI for the solving process, it is a compilation of random and intelligent search. These are stochastic algorithms, where search process works similarly to the processes that are responsible for evolution: inheritance and natural selection.

As an example, consider population of mice. There are fast, smart, slow and silly among them. Faster and smarter mice usually escape from the cat. Therefore, after some time, population of mice has majority of smart and fast, because other died. Of course some silly and slow mice also survive, because they are simply lucky. This population has an offspring. Next generation inherits genetic material from the parents and the children abilities are the mixture of fast, smart, slow and silly mice abilities. Mice become on average faster and smarter in every evolution step. Additionally nature introduces mutation of genes during reproduction, what results in mice with abilities, which were not present earlier in the population. Evolution in natural environment goes very slowly, because individuals from one generation need some time to be ready to contribute to the next generation and it is hard to notice any improvements in our surrounding. In computer memory individuals may be represented by binary chromosomes. These chromosomes may exchange information or undergo mutation. In this virtual world it is possible to speed up the process and use evolution to find problem solution. GAs description uses some terms straight from natural genetics [16].

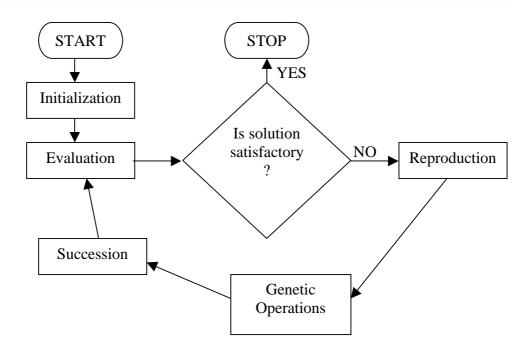

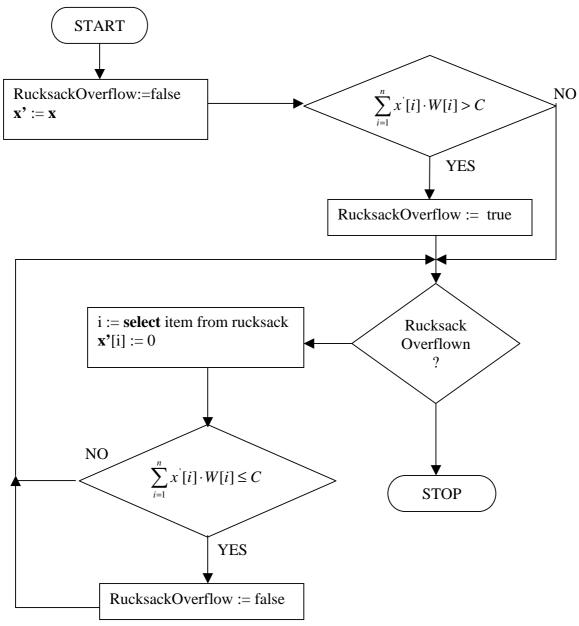

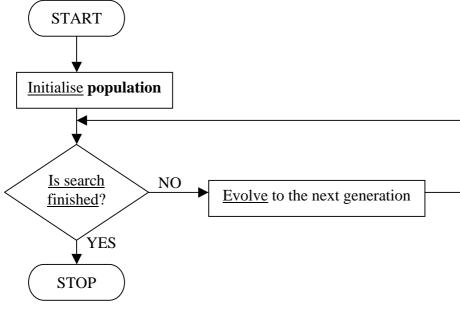

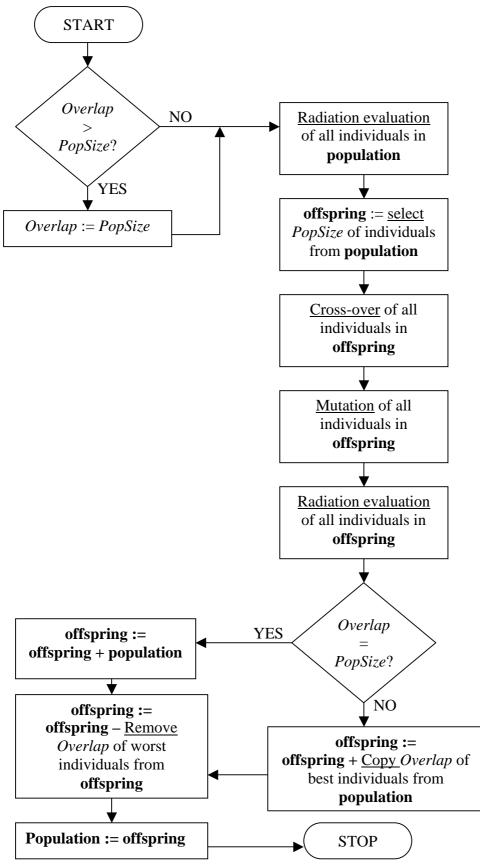

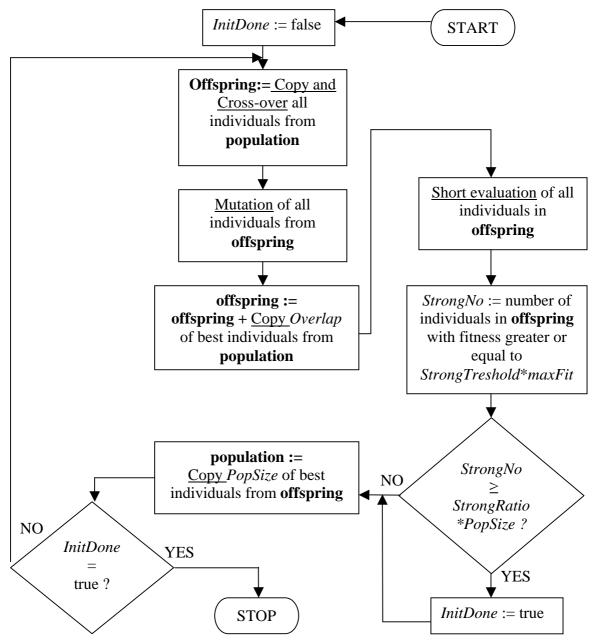

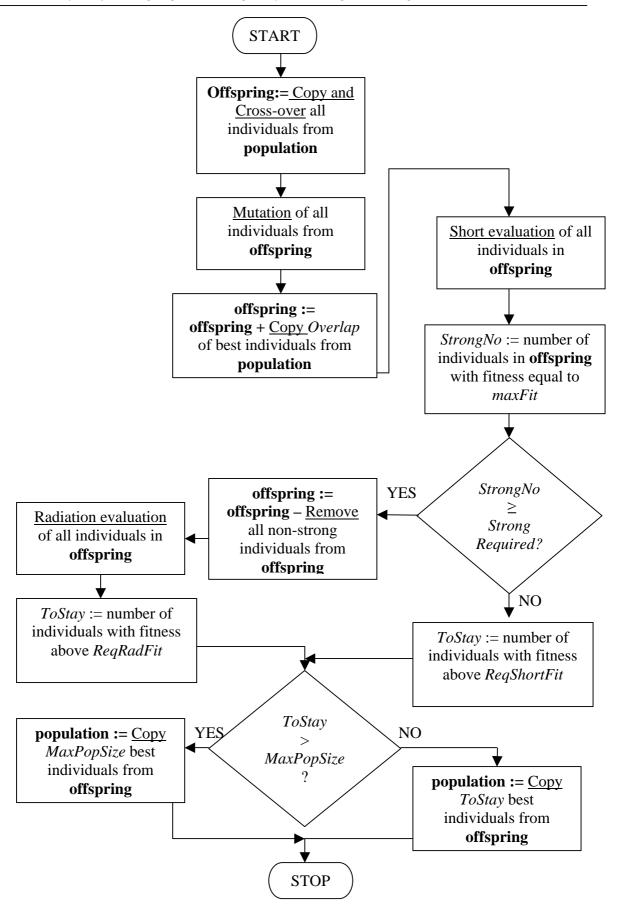

GA processes the population of **individuals**. Each of them is simply one of the possible solutions. Each individual is judged on the basis of **fitness function** value, which is the measure of goodness of the solution. The fitness function is constructed accordingly to the problem to be solved, it describes **environment** in which individuals are placed. The abilities, or in other words attributes of every individual are coded in its **genotype**, which in turn consists of **chromosome** or chromosomes. A chromosome consists of the elementary genetic units called **genes**. Values possible to represent by each gene are called **alleles**. Algorithm proceeds in iterations, creating new generation each time. Figure 3.1. presents basic GA loop.

Figure 3.1. General Genetic Algorithm schematic

**Initialisation** step involves creation of initial population of individuals. This is done by picking chromosomes at random. Each gene in each chromosome is selected at random from the alleles of the gene. For the binary chromosome alleles of the gene are "0" and "1".

**Evaluation** step involves calculation of fitness function value for each individual. After this step algorithm checks if best individual fulfils the solution requirements, if not, program goes on.

**Reproduction** step involves selection of individuals, which should contribute to the next generation. The intermediate generation is created. Selection can be done in variety ways, but should take into account value of fitness function of the individuals. In classic genetic algorithm, so called "Goldberg algorithm", roulette wheel selection mechanism is used, where each individual occupies space on the wheel proportional to its fitness. The probability of selecting the individual to the intermediate generation is proportional to the space occupied by the individual on the wheel. Equation (3.1) presents probability  $p_i$  of selecting  $v_i$  from pop\_size of population members.

$$p_{i} = \frac{fit(v_{i})}{\sum_{j=1}^{pop_{-}size} fit(v_{j})}$$

(3.1)

Therefore, best individuals usually place more than one copy in the intermediate population and worse have small chance to place any. This is similar to the natural selection.

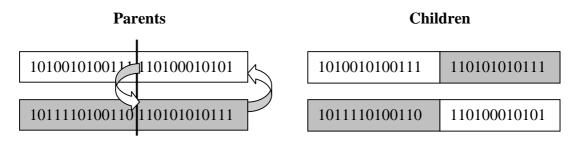

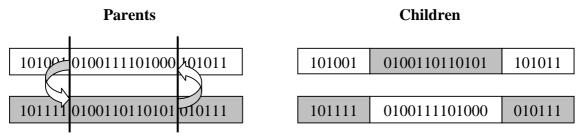

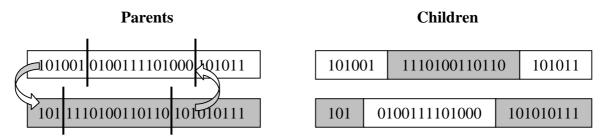

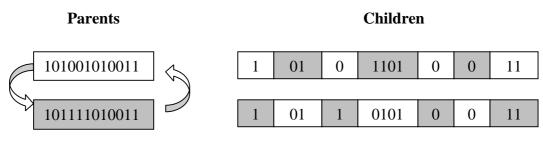

**Genetic Operations** step involves crossing-over and mutation. Crossing-over is genetic operator that usually creates two children from two parents, but there are different crossing operators and algorithm designer can invent new ones. The simplest one is one point crossing-over as presented in the Figure 3.2.

Figure 3.2. One point cross-over operation

The crossover position is picked at random, chromosomes are broken at this position and parts are swapped. One could think of two-point crossover, where there are two cross positions chosen randomly and parts between these positions are swapped or uniform crossover, where every gene in the child chromosome is taken from one or the other parent or even more complicated ones. Some exemplary crossover operators are described in section 3.1.4.

Next genetic operator is mutation. Mutation changes randomly chosen genes in the chromosome to other values chosen from possible alleles. In case of binary chromosome, this is simply a bit flip in the chromosome. It is worth mentioning that crossing-over does not necessarily need to be done for every pair of individuals in the intermediate population, it is done with some probability. The same applies to the mutation. The crossover probability and mutation probability are the basic parameters of the algorithm, which have to be wisely chosen, what requires some experience with GAs. Mutation probability is usually set to small value; the order of 1% or even less seems reasonable. Too much mutation may prevent algorithm from converging to the satisfactory solution, because each mutation introduces element of randomness, what usually worsens the solution, when algorithm approaches the right one. On the other hand, too small probability of mutation may let algorithm stuck in so-called evolution trap, which is simply local extremum of the optimised function. **Succession** involves replacement of old population by a new one. There are different methods to do that. It can be simple replacement: all new replace all old or more sophisticated like: few best old stay and the rest is chosen from the best new - so called "elitism". Here again, like in case of crossover operator, the imagination of the algorithm designer is the only limit.

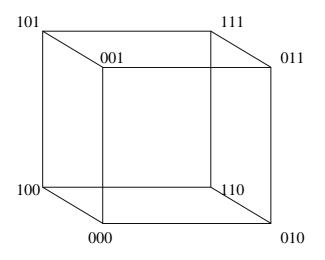

The explanation of GAs functioning bases on the representation of the solutions by chromosomes and on schemata [17]. Schemata are build using "don't care" symbol (usually \*) to the gene alphabet. Schema represents all chromosomes, which conform to it in all positions everywhere except \* positions, in other words it represents hyperplane in the search space. For example schema 10\*00 matches two strings 10000 and 10100, and schema 1\*0\*0 matches four strings: 10000, 10010, 11000, 11010. There are two terms connected with schemata, which need to be defined at this point, namely *schema order* and *defining length*. Schema order *o* is the number of symbols other than \* in the schema. For example schema 100\*0\* is of order 4, and schema 1\*\*\*\*\* of order 1. Schemata of higher orders are more specific; there are less strings that match them. Defining length  $\Delta$  is the distance between first and last specified symbol (not \* symbol). For example  $\Delta(1***0) = 5-1 = 4$ ,  $\Delta(****0) = 0$ ,  $\Delta(**11*) = 4-3 = 1$ . Defining length is useful in calculations of probability of survival of the schema after crossing-over. It is easier to understand hyperplanes by drawing them in 3D space. As an example

consider problem encoded with 3-bit chromosomes. The possible solutions form hypercube

as shown in the figure 3.3 [18].

Figure 3.3. 3-bit Hypercube

The corners are labelled by 3-bit chromosomes or solutions, where all adjacent corners differ by 1 bit. Every plane of the hypercube can be represented by a schema. For example front plane 0\*\*, back plane 1\*\*, top plane \*\*1, and so on. Assuming that binary chromosome encoding of the length m is used, every corner of the hypercube is a member of  $2^m - 1$  hyperplanes, \*\*\*...\*\*\* represents entire search space and is not counted as a hyperplane. The  $3^m - 1$  hyperplanes can be defined in the search space, because the 0, 1 or \* can be placed in m positions. Fact that one solution is a member of  $2^{m}$  -1 hyperplanes is the key part of GAs, because by examination of the single solution, many hyperplanes are sampled at the same time. The idea of searching for the perfect solution by means of population of possible points gives huge potential to the GAs, because in the population of n members  $n \cdot (2^m - 1)$  schemata can be represented. Thus, usually n members of population provide information on more hyperplanes than n. Furthermore, it is clear that hyperplanes represented by low order schemata are sampled by more solution points than high order. All above mention facts contribute to so called *implicit parallelism*, which is the true power of GAs [18]. Implicit parallelism means that upon evaluation of the population of chromosomes many hyperplanes are sampled at the same time. Every hyperplane contributes to the fitness function of the solution points, which lie on it. Chromosomes with higher fitness function value have higher probability of being selected to the next population and to enlarge its presence in the population, while those with lower value of fitness function usually are removed from the population. Therefore, more promising hyperplanes are sampled more and more precisely while less promising are forgotten.

An example can help to understand the hyperplane sampling. Consider 4-bit chromosomes. The fitness function value is simply the number of "1" in the chromosome. Fitness function value for the schema is defined as average of fitness values of all chromosomes matching given schema. Equation (3.2) defines fitness function value for the schema S, where t is current population time,  $v_{Sj}$  is the j-th string matching schema S, match function value is the number of all chromosomes matching schema S at time t.

$$fit(S,t) = \frac{\sum_{j=1}^{m} fit(v_{Sj})}{match(S,t)}$$

(3.2)

Table 3.1. presents fitness values for  $1^{***}$  and  $0^{***}$  hyperplanes.

| Schema | Fitness      | Schema | Fitness     |

|--------|--------------|--------|-------------|

| 1000   | 1            | 0000   | 0           |

| 1001   | 2            | 0001   | 1           |

| 1010   | 2            | 0010   | 1           |

| 1011   | 3            | 0011   | 2           |

| 1100   | 2            | 0100   | 1           |

| 1101   | 3            | 0101   | 2           |

| 1110   | 3            | 0110   | 2           |

| 1111   | 4            | 0111   | 3           |

| 1***   | 20 / 8 = 2.5 | 0***   | 12 / 8 =1.5 |

Table 3.1. Calculation of fitness function values for 1\*\*\* and 0\*\*\* hyperplanes

The hyperplane  $1^{***}$  seems more promising, because of higher fitness and therefore will increase its presence in the subsequent generations. Of course hyperplanes  $*1^{**}$ ,  $**1^{*}$  and \*\*\*1 have the same fitness and will also increase its presence. But this is just explanation of the idea and for the sake of simplicity, the consideration is limited to the hyperplane  $1^{***}$ . In the next step schemata of higher order, but representing hyperplane  $1^{***}$ , have to be considered. The fitness for hyperplane  $11^{**} = 12 / 4 = 3$ , and for hyperplane  $10^{**} = 8 / 4 = 2$ . Again going to the schemata of higher order, but representing hyperplane

$11^{**}$  we get: fitness for  $111^* = 7/2 = 3.5$ , and for  $110^* = 5/2 = 2.5$ . Finally 1111 = 4 and 1110 = 3. The final solution is 1111 with maximal fitness function value. In this example, the fitness function values for hyperplanes were determined precisely by calculating average of fitness function values for all solution points belonging the plane, what is obviously not the case in the real GA run, this would be pointless. In the real case only solution points present in the population sample the hyperspace and by selection of better chromosomes better hyperplanes are promoted. For example chromosome 1010 contains in its fitness function value contributions of the following hyperplanes:  $1^{**}$ ,  $*0^{**}$ ,  $*^{*1}$ ,  $*^{**0}$ ,  $10^{**}$ ,  $*01^*$ ,  $*^{*10}$ ,  $1^{*1*}$ ,  $1^{**0}$ ,  $*0^{*0}$ ,  $101^*$ , \*010,  $1^{*10}$ ,  $10^{*0}$ .

After selection we expect that match(S,t+1) chromosomes matches schema S. The probability of selecting the average chromosome matching schema S at time t is

$$p_{S} = \frac{fit(S,t)}{\sum_{j=1}^{pop_{-size}} fit(v_{j})}$$

(3.3)

Equation (3.3) is similar to the equation (3.1) for the probability of selecting a chromosome, but chromosome fitness is replaced with schema fitness. The number of chromosomes matching schema S is match(S,t). Number of opportunities (selections) is  $pop\_size$ . Collecting above-mentioned facts together, we can define the number of chromosomes matching schema S at time t+1 as

$$match(S,t+1) = match(S,t) \cdot pop\_size \cdot p_{S} = match(S,t) \cdot \frac{fit(S,t)}{\sum_{j=1}^{pop\_size} fit(v_{j})}.$$

$$(3.4)$$

$$\frac{\sum_{j=1}^{j=1} fit(v_{j})}{pop\_size}$$

(3.4) proves that number of chromosomes matching given schema changes proportionally to the ratio of the schemata fitness function value and the average population fitness function value. This means, that individuals evaluated above the average increase their presence, the average individuals do not change their number and individuals below the average will decrease their presence. This comes from the fact that  $\varepsilon > 1$  in (3.5) for schemata evaluated above average fitness function value,  $\varepsilon = 1$  for average,  $\varepsilon < 1$  for worse than average.

$$fit(S,t) = \varepsilon \frac{\sum_{j=1}^{pop\_size} fit(v_j)}{pop\_size}$$

(3.5)

By substitution in (3.4) by fit(S,t) from (3.5):

$$match(S,t+1) = match(S,t) \cdot \varepsilon$$

$$match(S,t) = match(S,0) \cdot \varepsilon^{t}$$

(3.6)

Now it is clear that schemata above the average gain more and more place in population, what is more, it is exponential gain [17].

Selection mechanism does not produce any new schemata or solution points; it just copies chromosomes to form intermediate population. This is done in the next step of evolution using crossover and mutation genetic operators. These operators obviously interfere with schemata copying, and the equation (3.4) has to be slightly modified to reflect the real behaviour. For simplicity, only one point crossover operator will be considered here. For example there are two schemata of length 10:

$$S_0 = ***101****$$

$S_1 = 11******0$

Assume, the crossover position is 7. Schema  $S_0$  survives the operation and  $S_1$  is destroyed. As mentioned earlier in this chapter, defining length is the parameter, which helps in probability of survival after crossing-over.  $\Delta(S_0) = 6-4=2$  and  $\Delta(S_1)=10-1=9$ . The crossover position can be selected from *m*-1 possibilities, thus the probability of schema destruction is:

$$p_d(S) = \frac{\Delta(S)}{(m-1)} \tag{3.7}$$

Thus, the probability of survival

$$p_s(S) = 1 - p_d(S) = 1 - \frac{\Delta(S)}{(m-1)}$$

(3.8)

However, not all chromosomes undergo crossover, but the crossover probability is  $p_c$ , therefore

$$p_s(S) = 1 - p_c \frac{\Delta(S)}{(m-1)}$$

(3.9)

In fact equation (3.9) should be inequality, because there is very small chance, that even though the crossover position is inside the schema like  $S_1$ , it will survive. This can be the case when the child inherits genes, which match the schema. Thus, after collecting selection and crossover mechanisms together equation (3.4) changes into:

$$match(S,t+1) \ge match(S,t) \cdot \frac{fit(S,t)}{\sum_{j=1}^{pop\_size} fit(v_j)} \cdot \left(1 - p_c \frac{\Delta(S)}{(m-1)}\right)$$

(3.10)

$$\frac{1}{pop\_size}$$

Mutation also can alter the schemata. The probability of changing single bit in the chromosome is  $p_m$ , thus probability of bit survival is  $1 - p_m$ . The number of positions in the chromosome relevant to the schema is the order of schema, so the probability of schema survival is:

$$p_s = (1 - p_m)^{o(S)} \tag{3.11}$$

since  $p_m$  is usually much, much smaller than 1 (3.11) can be approximated as:

$$p_s(S) \approx 1 - o(S) \cdot p_m \tag{3.12}$$

Thus, after collecting selection, crossover and mutation influence equation (3.4) becomes:

$$match(S,t+1) \ge match(S,t) \cdot \frac{fit(S,t)}{\sum_{\substack{pop_size\\j=1\\pop_size}}} \cdot \left(1 - p_c \frac{\Delta(S)}{(m-1)} - o(S) \cdot p_m\right)$$

(3.13)

Again, the conclusion is that the number of chromosomes representing schema evaluated above the population average is rising exponentially. But this has to be schema of small defining length and low order, because only then the destructive effect of mutation and crossover is not relevant. However, crossover and mutation operators are essential, because selection as such, does not introduce any new schemata into the population.

This is the basis for the Schemata Theorem.

# Short, low order schemata evaluated above the average get exponentially raising representation in the population. [17]

# 3.1.2. Pros and Cons of GAs

This section contains short summary of GAs properties divided into advantages and disadvantages.

## Advantages:

## • Easy to understand [19]

The basic concept of GAs is easy to understand, because it is based on natural selection and inheritance laws, which are easily explainable due to correspondence to real life situations

## Chromosome abstraction

The algorithm designer does not have to deal with parameters of the optimised function, does not have to change them directly or analyse relations between them. The basic idea is always the same: evaluation, selection, genetic operations and so on. Program works on chromosomes, which code the solution and thus provide solution abstraction.

## Multiparameter optimisation [19]

Programs based on GAs are capable of optimisation of many parameters at once. The possible combination of parameter values is represented as single fitness function value, which is optimised.

## Discrete functions optimisation

In case of discrete functions, analytical methods cannot be used, only stochastic ones are able to find the solution. GAs handle discrete and continuous functions without problems because of above-mentioned chromosome coding abstraction.

## Always provides the solution [19]

This statement at first seems questionable, but in fact from the first population the solution is available. It is not the best possible, but becomes better and better with time. This is not the truth when chromosome coding is chosen in a way, which allows for coding of individuals that are out of possible solutions set. This issue is discussed further in the section 3.2.3.

## Solution is sought in whole search space

The search for the best solution is started from many randomly chosen points in the search space and is then biased towards promising space points.

## Relatively easy in implementation

The implementation requires only the following elements:

- Population container the container for individuals, together with their genetic material

- o Genetic operations selection, cross-over and mutation

- o Fitness function implementation

Moreover, implementation does not consume memory for history keeping, like in ordinary stochastic algorithms. The "wisdom" of the population is incorporated into the genetic material of the individuals.

# Flexibility

Once implemented, the program can be easily changed for totally different problem. As long as the physical structure of the chromosome stays the same the only element that must change is fitness function, because this is the only part that deals with logical chromosome structure.

# Easy to distribute [19]

Selection is the only step, which needs knowledge of the whole population, all other operations require only information that they directly act on (usually chromosomes). Therefore, the program is easily distributable, many computers may work on the solution of single problem.

# May be improved as knowledge on the problem is gained

As knowledge on the problem domain is gained, chromosome coding and fitness function can be easily adjusted to reflect the problem more precisely and speed up the solution search.

## **Disadvantages:**

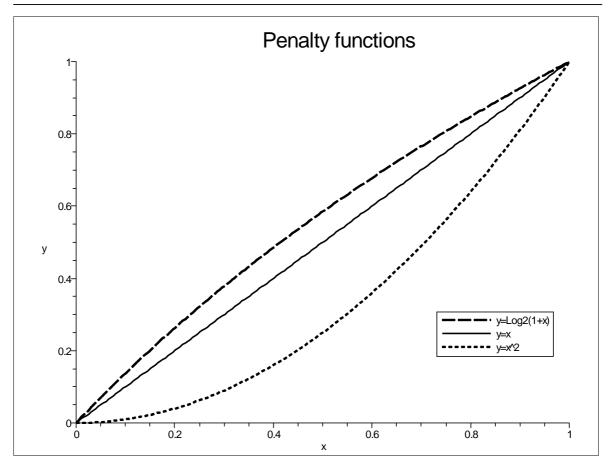

# • Choice of representation and fitness function is critical [19]

The hardest task for the algorithm designer is to choose appropriate chromosome-solution correspondence and fitness function. Chromosome should be able to code all possible solutions of the problem, but prevent coding of solution that lies outside the acceptable set. Fitness function has to take into account all of the goals algorithm has to achieve, and find good balance between them, what leads to simultaneous optimisation of all parameters. In fact determination of chromosome coding and fitness function are critical parts of the whole application. There are some attempts to theoretically describe the right way