## DSP Integrated, Parameterized, FPGA Based Cavity Simulator & Controller for VUV-FEL

# SC Cavity SIMCON

### version 2.1. rev. 1, 02.2005

## **USER'S MANUAL**

Krzysztof T. Pozniak, Tomasz Czarski, Waldemar Koprek, Ryszard S. Romaniuk pozniak@mail.desy.de; tczarski@ntmail.desy.de; wkoprek@ntmail.desy.de, rrom@mail.desy.de

Institute of Electronic Systems, Warsaw University of Technology, ELHEP Group Nowowiejska 15/19, 00-665 Warsaw, Poland

#### ABSTRACT

The note describes integrated system of hardware controller and simulator of the resonant superconducting, narrowband niobium cavity, originally considered for the TTF and TESLA in DESY, Hamburg (now predicted for the VUV and X-Ray FEL). The controller bases on a programmable circuit Xilinx VirtexII V3000 embedded on a PCB XtremeDSP Development Kit by Nallatech. The FPGA circuit configuration was done in the VHDL language. The internal hardware multiplication components, present in Virtex II chips, were used, to improve the floating point calculation efficiency. The implementation was achieved of a device working in the real time, according to the demands of the LLRF control system for the TESLA Test Facility. The device under consideration will be referred to as superconducting cavity (SCCav) SIMCON throughout this work..

The following components are described here in detail: functional layer, parameter programming, foundations of control of particular blocks and monitoring of the real time processes. This note is accompanied by the one describing the DOOCS interface for the described hardware system. The interface was prepared in DOOCS and in Windows. The hardware and software of SIMCON was tested in CHECIA. The results were presented.

While giving all necessary technical details required to understand the work of the integrated hardware controller and simulator and to enable its practical copying, this document is a unity with other TESLA technical notes published by the same team on the subject. Thus, some modeling and other subjects were omitted, as they were addressed in detail in the quoted references.

**Keywords**: Super conducting cavity, cold option, cavity simulator, cavity controller, linear accelerators, FPGA, FPGA-DSP enhanced, VHDL, FEL, TESLA, TTF, UV-FEL, Xilinx, FPGA based systems, LLRF control system of third generation, electronics for UV-FEL, X-Ray FEL and TESLA.

Acknowledgement: We acknowledge the support of the European Community Research Infrastructure Activity under the FP6 "Structuring the European Research Area" program (CARE, contract number RII3-CT-2003-506395)

## MAJOR CHANGES FROM SIMCON VERSION 1.0, REV. 1, 04.2004

Published as TESLA FEL Report 2004-04

- Automatic switching of parameters and tables was added. The switching enables control parameter changes without stopping, resetting or switching off the SIMCON. This change was presented in paragraph 7.2.3.,

- An input compensation matrix was added to the algorithm of the cavity controller. This change was described in paragraph 7.2.5.,

- The access rules to the tables have been changed. This change was described in paragraph 3.2.

- Two options for the voltage range of the cavity Simulator were introduced. This change was described in paragraph 7.2.4.

- The dimensions in bits of the tables for amplification values for cavity controller and beam current values for cavity simulator were equalized. The equalization enables realization of automatic switching mechanism. This change was described in paragraph 7.2.3.

- An additional VMEbus interface was added. This change was described in Annex 13.

- A number of representative exemplary results from SIMCON tests with CHECHIA were added. The results are presented in Annex F.

- Many tables and figures were updated and renumbered throughout the whole text.

## CONTENTS

| 1 | CAV                                  | VITY SIMULATOR AND CONTROLLER ALGORITHM                                                 | 5  |  |  |  |

|---|--------------------------------------|-----------------------------------------------------------------------------------------|----|--|--|--|

|   | 1.1                                  | CAVITY SIMULATOR ALGORITHM                                                              |    |  |  |  |

|   | 1.2<br>1.3                           | CAVITY CONTROLLER ALGORITHM                                                             |    |  |  |  |

| • |                                      |                                                                                         |    |  |  |  |

| 2 | GENERAL DESCRIPTION OF SIMCON SYSTEM |                                                                                         |    |  |  |  |

|   | 2.1                                  | HARDWARE STRUCTURE                                                                      |    |  |  |  |

|   | 2.2                                  | FUNCTIONAL STRUCTURE                                                                    |    |  |  |  |

| 3 | STATUS CONTROLLER BLOCK DESCRIPTION  |                                                                                         |    |  |  |  |

|   | 3.1                                  | FUNCTIONAL DESCRIPTION                                                                  |    |  |  |  |

|   | 3.2                                  | PROGRAMMING DESCRIPTION                                                                 |    |  |  |  |

|   |                                      | 3.2.1 INTERNAL mode operation                                                           |    |  |  |  |

|   |                                      | <ul><li>3.2.2 EXTERNAL mode operation</li><li>3.2.3 VECTOR mode operation</li></ul>     |    |  |  |  |

|   |                                      | <ul><li>3.2.3 VECTOR mode operation</li><li>3.2.4 STEP mode operation</li></ul>         |    |  |  |  |

|   |                                      | 1                                                                                       |    |  |  |  |

| 4 |                                      | IING CONTROLLER BLOCK DESCRIPTION                                                       |    |  |  |  |

|   | 4.1                                  | FUNCTIONAL STRUCTURE                                                                    |    |  |  |  |

|   | 4.2                                  | CAVITY TIMING MULTIPLEXER DESCRIPTION                                                   |    |  |  |  |

|   | 4.3                                  | PROGRAMMING DESCRIPTION                                                                 |    |  |  |  |

|   |                                      | <ul><li>4.3.1 Internal timing generation</li><li>4.3.2 Step operation process</li></ul> |    |  |  |  |

|   |                                      | 4.3.3 Time adjustment of the trigger signals                                            |    |  |  |  |

| 5 | INP                                  | UT PROCESSING BLOCK DESCRIPTION                                                         |    |  |  |  |

|   | 5.1                                  | FUNCTIONAL STRUCTURE                                                                    | 19 |  |  |  |

|   | 5.2                                  | PROGRAMMING DESCRIPTION                                                                 |    |  |  |  |

| 6 | OU                                   | <b>FPUT PROCESSING BLOCK DESCRIPTION</b>                                                | 21 |  |  |  |

|   | 6.1                                  | FUNCTIONAL STRUCTURE                                                                    |    |  |  |  |

|   | 6.2                                  | PROGRAMMING DESCRIPTION                                                                 |    |  |  |  |

| 7 | PRO                                  | DGRAMMABLE DATA CONTROLLER                                                              | 22 |  |  |  |

|   | 7.1                                  | FUNCTIONAL STRUCTURE                                                                    |    |  |  |  |

|   | 7.2                                  | PROGRAMMING DESCRIPTION                                                                 |    |  |  |  |

|   | /                                    | 7.2.1 Dynamic data multiplexer                                                          |    |  |  |  |

|   |                                      | 7.2.2 Modulator driver                                                                  |    |  |  |  |

|   |                                      | 7.2.3 Data switching                                                                    | 24 |  |  |  |

|   |                                      | 7.2.4 Cavity simulator programmable data packet                                         |    |  |  |  |

|   |                                      | 7.2.5 Cavity controller programmable data packet                                        | 25 |  |  |  |

| 8 | CAV                                  | VITY SIMULATOR BLOCK DESCRIPTION                                                        | 26 |  |  |  |

|   | 8.1                                  | FUNCTIONAL STRUCTURE                                                                    | 26 |  |  |  |

|   | 8.2                                  | PROGRAMMING DESCRIPTION                                                                 | 27 |  |  |  |

| 9  | CAVITY CONTROLLER BLOCK DESCRIPTION                       |    |

|----|-----------------------------------------------------------|----|

|    | 9.1 FUNCTIONAL STRUCTURE                                  |    |

|    | 9.2 PROGRAMMING DESCRIPTION                               |    |

| 10 | DATA ACQUISITION (DAQ) BLOCK DESCRIPTION                  |    |

|    | 10.1 Functional structure                                 |    |

|    | 10.2 PROGRAMMING DESCRIPTION                              |    |

|    | 10.2.1 DAQ modes control                                  |    |

|    | 10.2.2 DAQ memory access                                  |    |

|    | 10.2.3 DAQ readout process<br>10.2.4 DAQ vector generator |    |

| 11 |                                                           |    |

| 11 | INPUT MULTIPLEXERS BLOCK DESCRIPTION                      |    |

|    | 11.1 FUNCTIONAL STRUCTURE                                 |    |

|    | 11.2 PROGRAMMING DESCRIPTION                              |    |

| 12 | OUTPUT SWITCH MATRIX BLOCK DESCRIPTION                    |    |

|    | 12.1 FUNCTIONAL STRUCTURE                                 |    |

|    | 12.2 PROGRAMMING DESCRIPTION                              |    |

| 13 | PROGRAMMABLE I/O SPECIFICATION                            |    |

|    | 13.1 I/O SPECIFICATION LIST BY ADDRESSES                  | 38 |

|    | 13.2 I/O SPECIFICATION LIST BY NAMES                      |    |

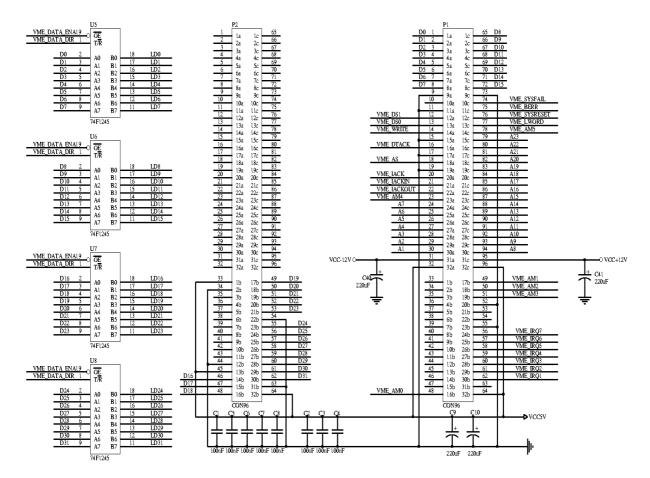

| A  | VME INTERFACE                                             |    |

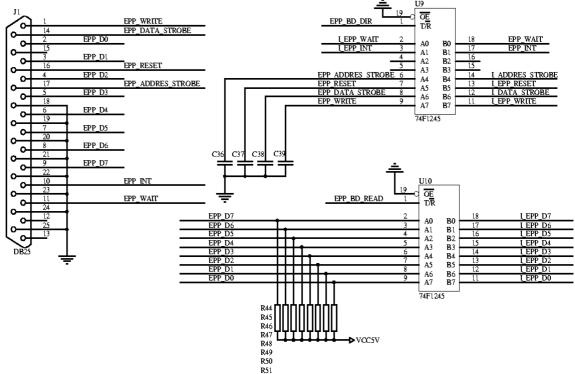

| B  | EPP INTERFACE                                             |    |

| С  | BENONE OVERVIEW                                           |    |

| D  | BENADDA OVERVIEW                                          |    |

| Ľ  |                                                           |    |

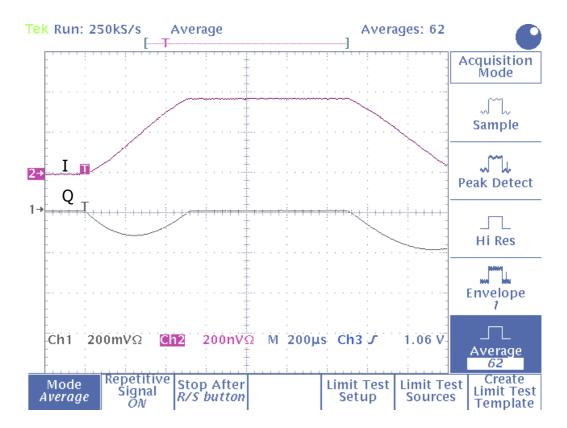

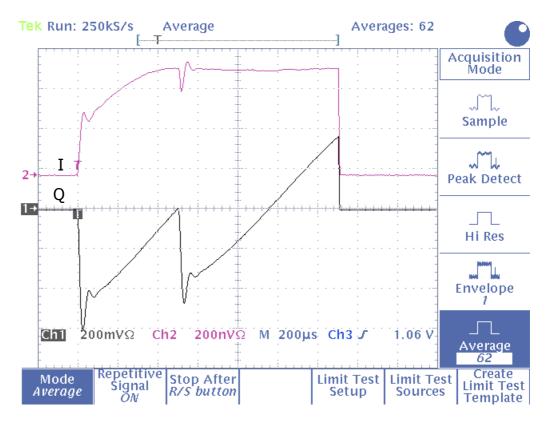

| Ε  | EXEMPLARY SCOPE PICTURES OF SIMCON SYSTEM OUTPUTS         |    |

| F  | EXEMPLARY RESULTS OF CHECHIA REAL-TIME CONTROL            | 67 |

#### 1 CAVITY SIMULATOR AND CONTROLLER ALGORITHM

The cavity resonator modeling has been developed for the efficient testing of the control system and for the investigation of the optimal control method. The software models allow for testing of the hardware controller by the step operation mode. The FPGA hardware implementation of the cavity model is intended for the real time operation.

#### 1.1 Cavity simulator algorithm

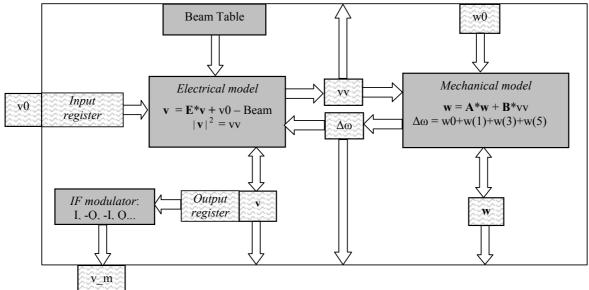

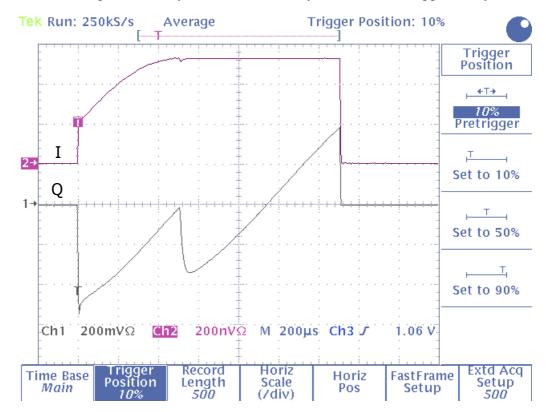

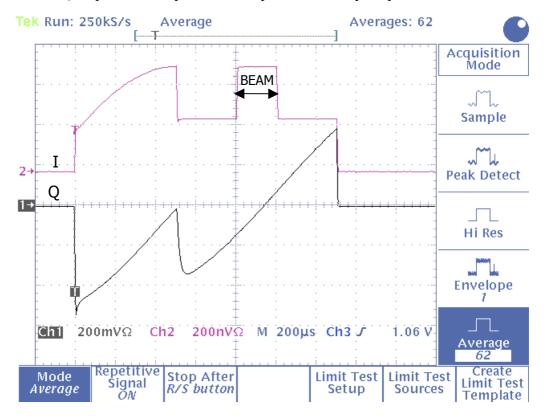

The cavity electromechanical model including Lorentz force detuning and the beam loading is applied for analyzing the basic features of the plant. The cavity control system proceeds within the low-level frequency range of the *complex envelope* for the input current and output voltage of the cavity. The *complex envelope* signal is represented by real (I – in-phase) and imaginary (Q – quadrature) components. The discrete processing of the cavity behavior has been developed for the digital implementation of the cavity model. The functional diagram of the cavity simulator algorithm is presented in fig. 1.

Fig. 1. The functional diagram of the cavity simulator algorithm.

The electrical part of the cavity simulator consists of the DSP function block. The DSP procedure is realized according to the *state space* relation with the state vector v representing (I, Q) components of the cavity output *envelope*. The system matrix E depends on the cavity detuning  $\Delta \omega$  and the cavity bandwidth only. The normalized current generator as the input signal  $v_0$  and the beam from the table drives the DSP unit. Additionally, the non-stationary detuning  $\Delta \omega$  modulates the object feature by the matrix E. The square of the cavity field gradient  $|v|^2 = vv$  drives the mechanical part of the model. The input and output registers correspond to the time delay of the cavity environment (waveguide). The intermediate frequency modulator converts the cavity output vector to the signal v\_m of frequency 250 kHz. Therefore, the data samples, like from the down-converter, can be conveyed to the outer digital controller.

The mechanical model of the super-conductive cavity consists of the DSP unit according to the *state space* relation with the state vector **w**. The time-varying detuning  $\Delta \omega$  and its time derivative are two state-variables for each mechanical mode. The system matrix **A** and the input matrix **B** depend on the cavity parameters: resonance frequency, quality factor and Lorentz force-detuning constant for each mechanical mode. Each of the mechanical modes is driven by the square of the cavity field gradient vv generated from the electrical part of the

model. Three dominating resonance frequencies are considered in the cavity model and the superposition of all modes, together with the initial *predetuning*  $w_0$ , yield the resultant detuning  $\Delta \omega$ .

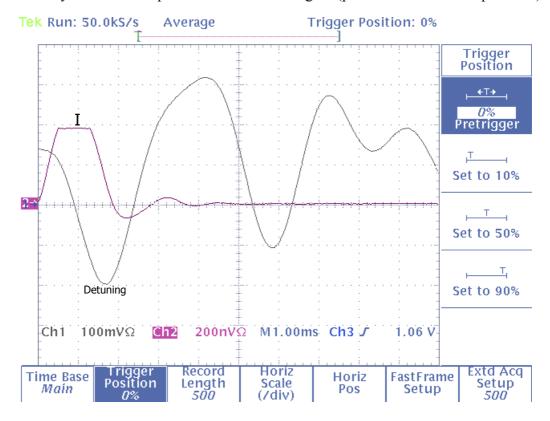

#### 1.2 Cavity controller algorithm

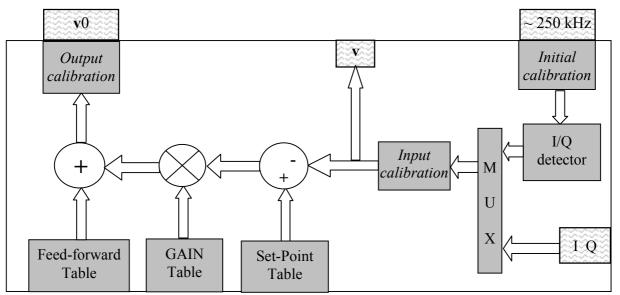

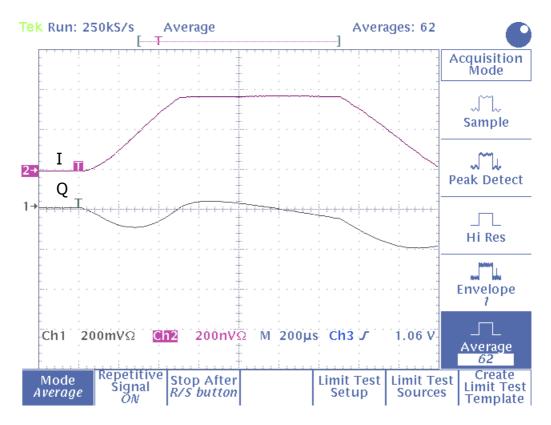

The comprehensive model of the control system has been developed to investigate different operational conditions of the cavity. The functional diagram of the controller algorithm is presented in fig. 2.

Fig. 2. The functional diagram of the controller algorithm

The digital processing is performed in I/Q detector applying the signal  $v_m$  of intermediate frequency 250 kHz from the cavity simulator. Additionally the (I, Q) vector can be directly accepted by MUX switch. The resultant cavity voltage *envelope* (I, Q) is calibrated in the next unit, so to compensate the measurement channel attenuation and phase shifting for an individual cavity. The Set-Point table delivers the required signal level, which is compared to the actual cavity voltage. The multiplier as the proportional controller amplifies the signal error according to data from the GAIN table and closes the feedback loop. Additionally the Feed-Forward Table is applied to improve compensation of the repetitive perturbations induced by the beam loading and by the dynamic Lorentz force detuning. The resultant output signal  $v_0$  can drive the cavity simulator.

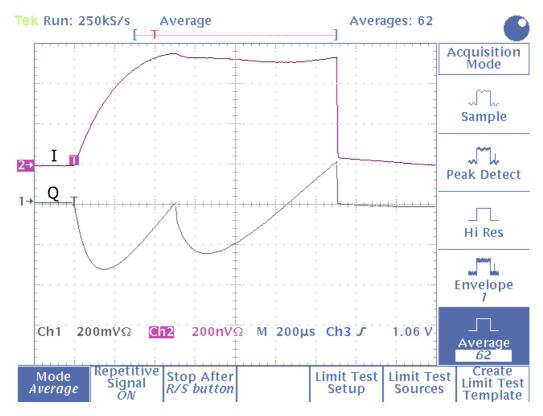

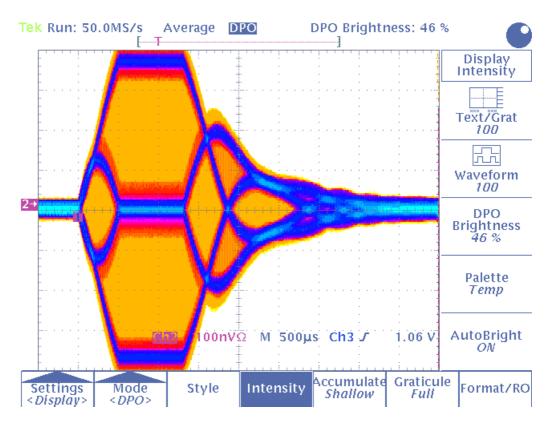

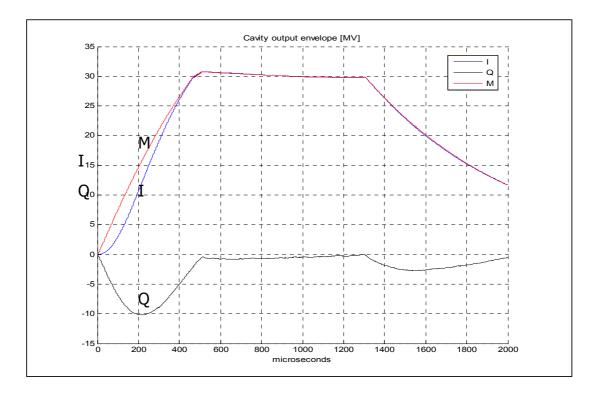

#### 1.3 Simulation procedure

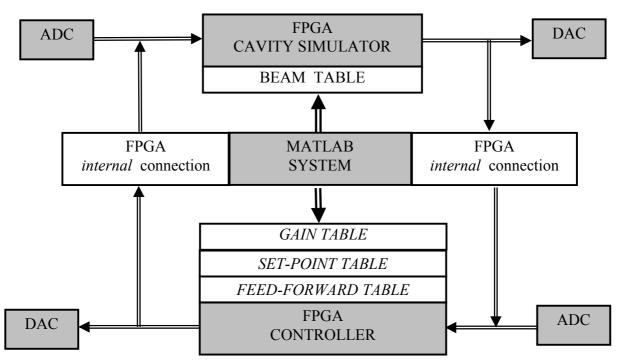

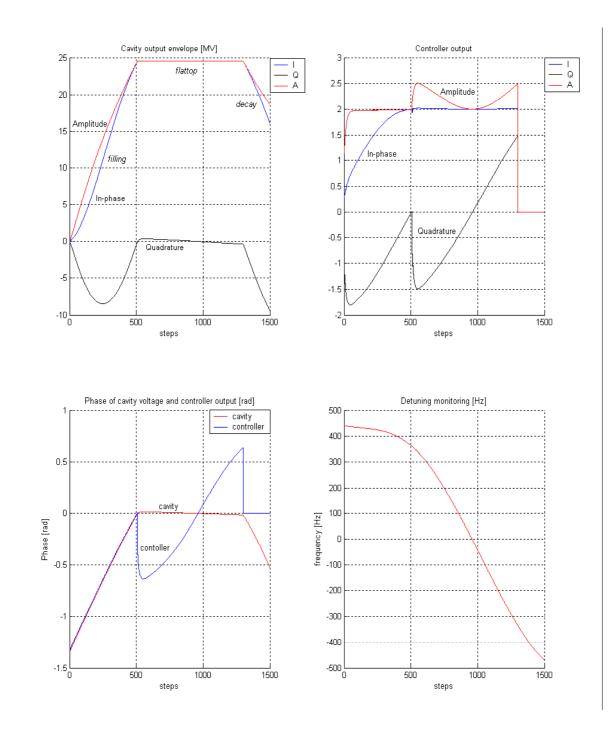

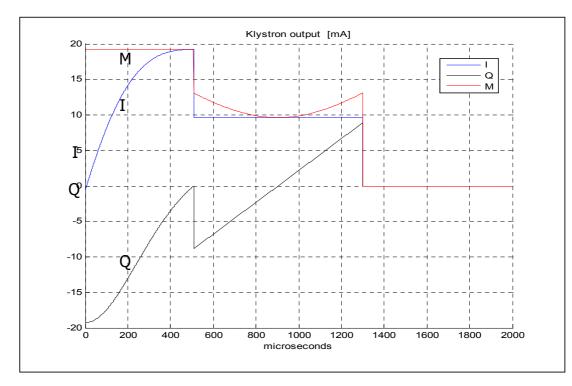

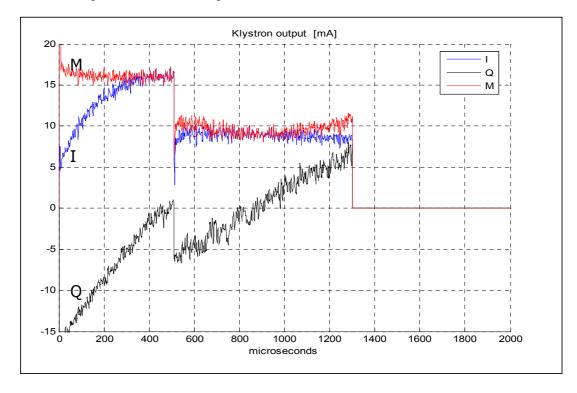

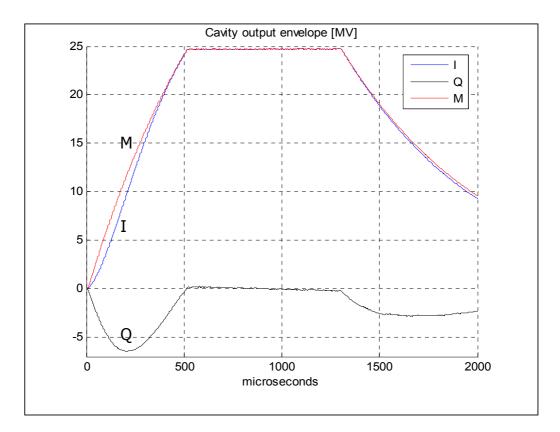

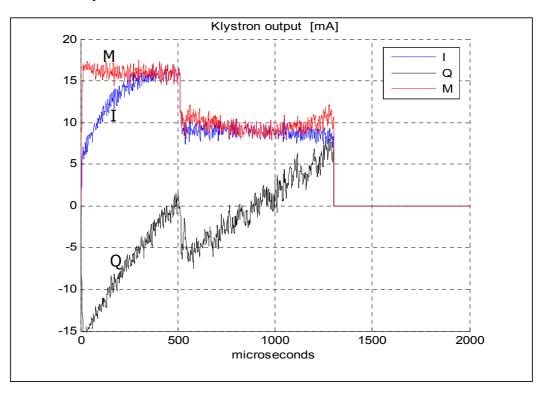

The FPGA cavity simulator and controller are coupled to the MATLAB system via communication interface. The real time tests are carried out according to the schematic block diagram in fig. 3. The MATLAB system initiates the simulation process for the given primary parameters. The list of parameters for user utility is combining in the table below. The secondary, internal parameters required for the FPGA system are calculated in the beginning. Additionally the optimal data for Set Point and Feed Forward tables are generated during the auto calibration process. Finally, the MATLAB simulation process is verified by plot. The resulting example, for the real operational condition, is presented in fig 4. The cavity is driven in the pulse mode forced by the control feedback supported by the feed forward.

Subsequently, resultant parameters and data are loaded to the FPGA memory tables. The cavity simulator and controller can be driven independently via the external connection

applying the analog-to-digital converters (ADC- 14-bit resolution). On the other hand, the FPGA controller can drive the FPGA cavity simulator via internal digital connection (18-bit data resolution). Then, the FPGA system can run itself cyclically according to the given data tables (see below). The digital-to-analog converter (DAC) conveys data from the FPGA cavity simulator or from the FPGA controller outside the system.

Tables of the primary parameters for the user utility.

Fig. 3. Functional diagram for one chip FPGA system

Fig. 4. The MATLAB results of simulation for real operation condition

#### 2 GENERAL DESCRIPTION OF SIMCON SYSTEM

The integrated and parameterized controller and simulator system for the resonant, superconducting, narrowband cavity of the UV-FEL (SIMCON) was implemented in a programmable FPGA chip Virtex II V3000. The chip has inbuilt hardware DSP components [8]. This chapter presents in a general way the functional and hardware structure of the device.

#### 2.1 Hardware structure

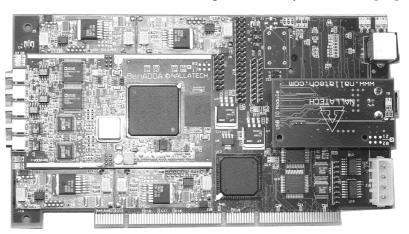

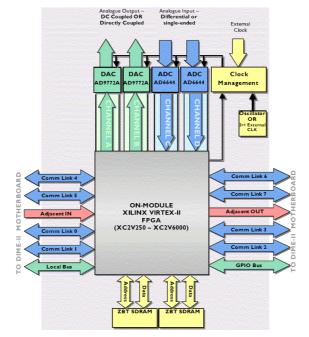

The hardware layer was realized with XtremeDSP Development Kit by Nallatech [12].

The version of the main board (MB) was BenONE with integrated daughter board (DB) BenADDA (fig.5) The DB is realizing hardware DSP algorithms. The DB possesses two fast 14-bit and DAC ADC and а programmable FPGA Xilinx V3000-4 VirtexII chip equipped in 18x18 bit multiplication circuits.

Adaptation of the *XtremeDSP Development Kit*

Fig. 5. XtremeDSP Development Kit by Nallatech

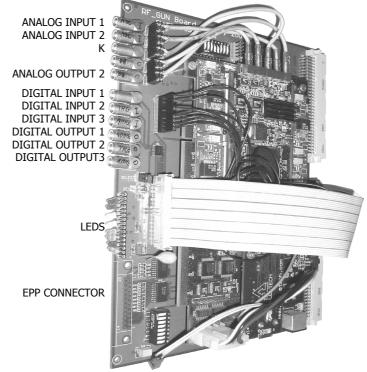

to the needs of the user in the EURO 6HE standard was realized by embedding on a dedicated base carrier board *6HE-EURO-VME/EPP*, what was presented in fig. 6. The front-side of the board possesses:

- Two analog inputs of the signals, with the signal range  $\pm 1V$ . Each channel signal is processed nondependently by a 14-bit ADC converter, working with 40MHz clock;

- Input of an external clock, for TTL standard;

- Two analog signal outputs with the signal range ±1V. Each channel signal is processed nondependently by a 14-bit DAC converter, working with 40MHz clock.

- Three digital inputs and three digital outputs in TTL standard, connected to the FPGA Virtex II via a suitable buffer;

- Two information LEDs;

- Socket for a parallel interface in EPP standard for communication of FPGA Virtex II with a control PC;

Fig. 6. XtremeDSP Development Kit embedded on a carrier board EURO-6HE.

The SIMCON card occupies two slots in the VME 6U crate. Power supply is provided either from the VME bus or from the power unit provided with the Nallatech board.

Application of the VME bus [9] stems from the requirements imposed by the DOOCS system [1]. The DOOCS is obligatory GUI to control the accelerator of the FEL. The access was realized in the A24D32 mode. There are 24 lines of address bus and 32 lines of data bus. The access is *SLAVE* for AM=39H and *MASTER* for AM=3DH [9]. The base address of the PCB in the address space of the VME bus is defined by the 4 oldest address bits (A23-A20). The appendix 13 describes the implemented VME bus interface.

The application of the EPP protocol to communicate with the computer is excused by the low throughput of the proprietary USB. Ver.1. offered by the board manufacturer. The choice of the EPP protocol is justified by its comparably high transmission speed, simplicity and popularity in the PC computers. The EPP protocol has a simple implementation in the FPGA chip. The hardware realization of the interface was described in detail in [2, 12]. The appendix B describes the technical realization of the EPP interface.

#### 2.2 Functional structure

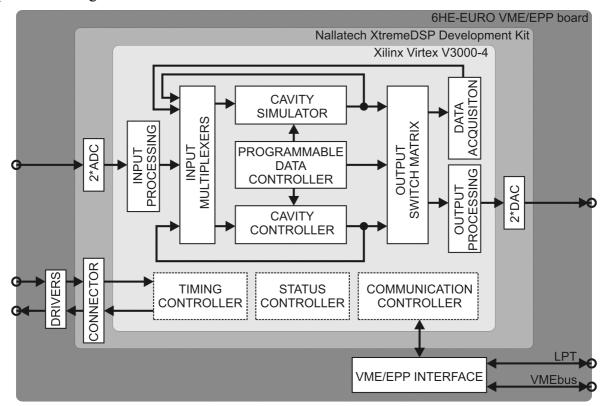

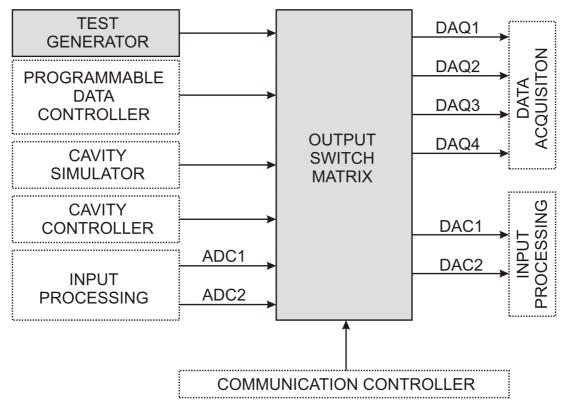

Integrated SIMCON system was realized in the form of parameterized structure of (Very High Speed Integrated functional blocks the language in VHDL Circuit Hardware Description Language). The implemented code was loaded in the Xilinx VirexII V3000-4 chip on the XtremeDSP Development Kit board. There were used the AD and DA converters situated on the BenADDA daughter board. The optional connection of the external control to the simulator or controller of the FEL cavity is possible. The digital TTL inputs present on the base board 6HE-EURO-VME/EPP were used for synchronization with the 1MHz clock and 5 Hz trigger. These signals are distributed in the whole control system of the FEL. An overall functional structure of the SIMCON, implemented in ver.1.0 was presented in fig. 7.

Fig. 7. Multi-Layered hardware and functional structure of the SIMCON

The solution applied in the SIMCON system bases on the backbone of parameterized and programmable blocks of parallel processing.

The core is constructed of two nondependent modules CAVITY SIMULTOR and CAVITY CONTROLLER. They were programmed inside the FPGA Virtex II 3000-4 chip as hardware DSP algorithms. The algorithms use fast internal multiplication components. The blocks work in parallel in the real time. They are controlled by programmable parameters provided by the PROGRAMMABLE DATA CONTROLLER block. The parameters are scalars (like parameters of the cavity and controller) and vectors (like the feed-forward for cavity controller, beam of cavity simulator). The set parameters stem from the algorithms described in detail in the following papers [4,6,7].

The block of INPUT MULTIPLEXERS serves for programmable choice of the control signals of the controller and simulator blocks. The realization of the following functions is possible through this functionality: internal digital feedback loops, connection of external analog signals from the AD converters, set test vectors initially programmed in the DAQ block. The task for the OUTPUT SWITCH MATRIX block is a programmable choice of the signals outputs for the DA converters or signal registration in the DAQ block. A suitable configuration of the switching matrices gives appropriate analog feedback between the modules of cavity controller and simulator

The block TIMING & STATUS CONTROLLER provides internal synchronization of the all processes of SIMCON system. It is possible to choose the external clock signals provided by the accelerator control system or from the external generators. The latter case enables autonomous work of the system. Switching of the work states of the system is possible, i.e. performing of processes in real time or in step simulation regime with reference vectors.

The programming layer of all the blocks of SIMCON system is realized by the control computer system with the aid of COMMUNICATION CONTROLLER block. The EPP hardware transmission protocol was used. The information distribution bases on the *Internal Interface* standard, described in detail in [2,8].

#### 3 STATUS CONTROLLER BLOCK DESCRIPTION

The SIMCON system may work in several work states (called operation modes). It provides possibility to realize various functionalities in a single integrated system. The work states are: autonomous, cooperation with external timing systems, functional tests state, diagnostic state and system programming state. Inside each operation mode two work states are available SETUP and RUN.

#### 3.1 Functional description

The block STATUS CONTROLLER manages the work states of the SIMCON system. From the operation point of view, setting of a particular work state has a superior character. There are distinguished four system work states in the SIMCON:

- *INTERNAL* the work in the real time mode is possible with the usage of internal timing signals (see chapter 4.2, 4.3.1)

- *EXTERNAL* the work in the real time mode is possible with the usage of external timing signals (see chapter 4.2)

- *VECTOR* the work is possible in the real time mode with internal timing signals and set exciting vectors (see chapter 4.2, 10.2.4)

- *STEP* the work is possible in the step operation mode with the usage of internal timing and programmable set input exciting data, separately for each step (see chapter 4.2, 4.3.2)

Each of the above modes has *SETUP* stage. The *SETUP* enables full programmers approach to the spaces of registers and memory through COMMUNICATION CONTROLLER. Each of the above modes has *RUN* mode. The *RUN* realizes functionalities of the system mode.

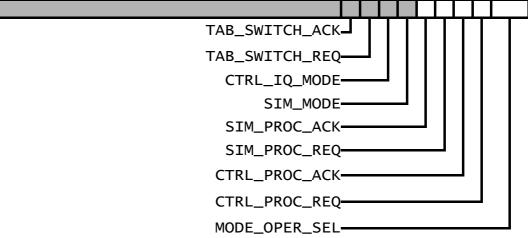

#### 3.2 Programming description

The choice of the system work mode is set with the aid of the register: MODE\_OPER\_SEL. The register has the following values:

- value 0 *INTERNAL* work mode is chosen (compare paragraph 3.2.1),

- value 1 *EXTERNAL* work mode is chosen (compare paragraph 3.2.2),

- value 2 *VECTOR* work mode is chosen (compare paragraph 0),

- value 3 *STEP* work mode is chosen (compare paragraph 3.2.4),

The flag CTRL\_PROC\_REQ enables, for the block CAVITY\_CONTROLLER, enables the choice between activation or programming of tables for the cavity controller inside the block of PROGRAMMABLE\_DATA\_CONTROLLER. It also allows activation of static values (compare paragraph 7.2.5). The acknowledgement of setting the required work state is done through reading the identical logical state of the flag CTRL\_PROC\_ACK:

• CTRL\_PROC\_REQ=0 and CTRL\_PROC\_ACK=0 causes switching of tables TSETPOINT\_I, TSETPOINT\_Q, TFEEDFORWARD\_I, TFEEDFORWARD\_Q, TGAIN\_I and TGAIN\_Q to the access of memory programming by the user via the block COMMUNICATION CONTROLLER. It also causes automatic activation of respective static registers: SSETPOINT\_I, SSETPOINT\_Q, SFEEDFORWARD\_I, SFEEDFORWARD\_Q, SGAIN\_I and SGAIN\_Q.

• CTRL\_PROC\_REQ=1 and CTRL\_PROC\_ACK=1 causes connection of tables TSETPOINT\_I, TSETPOINT\_Q, TFEEDFORWARD\_I, TFEEDFORWARD\_Q, TGAIN\_I and TGAIN\_Q to the cavity controller. The values of the static registers SSETPOINT\_I, SSETPOINT\_Q, SFEEDFORWARD\_I, SFEEDFORWARD\_Q, SGAIN\_I and SGAIN\_Q are ignored.

The flag SIM\_PROC\_REQ enables, for the block CAVITY SIMULATOR, a choice of activation or programming of tables in the block PROGRAMMABLE DATA CONTROLLER and respectively activation of the static values (compare chapter 7.2.4). The acknowledgement of the setting of required state is done through reading of identical logical state of the flag SIM\_PROC\_ACK:

- SIM\_PROC\_REQ=0 and SIM\_PROC\_ACK=0 causes table switching TBEAM\_I and TBEAM\_Q to the access of memory programming by the user via the block COMMUNICATION CONTROLLER. It also causes automatic activation of respective static register: SBEAM\_I and SBEAM\_Q.

- SIM\_PROC\_REQ=1 and SIM\_PROC\_ACK=1 causes connection of the tables TBEAM\_I and TBEAM\_Q to the cavity controller. The values of the static registers SBEAM\_I and SBEAM\_Q are ignored.

The request to change the flag state CTRL\_PROC\_REQ or SIM\_PROC\_REQ should result in respective change in the state of CTRL\_PROC\_ACK or SIM\_PROC\_ACK during the **time period of 100ns**.

The programming conditions for particular work states are described below in the successive sub-chapters.

#### 3.2.1 INTERNAL mode operation

In the *INTERNAL* work state the system is fully real-time and totally autonomous with the internal triggering signals and control tables (compare paragraphs 7.2.3 and 7.2.5).

#### 3.2.2 EXTERNAL mode operation

In the *EXTERNAL* mode of operation the outside timing signals are used in the TTL standard (compare chapter 4.1). The signals are respectively connected to the LEMO sockets (compare chapter 2.1):

- EXTERNAL CAVITY STROBE connected to DIGITAL INPUT 2,

- EXTERNAL CAVITY TRIGGER connected to DIGITAL INPUT 3.

From the programming steering side, the *EXTERNAL* operation mode is considerably identical with the *INTERNAL* operation mode (compare chapter 3.2.1). Additional functionality is the possibility to adjust external clock signals via the modules *CAVITY STROBE DELAY* and *CAVITY TRIGGER DEL* in block **TIMING CONTROLLER** (compare chapter 4.3.3).

#### **3.2.3 VECTOR mode operation**

The *VECTOR* mode operation uses internal memories DAQ1.. DAQ3 implemented in the block DATA ACQUISITION as programmable input signal generators (compare chapter 10.2.4). By the choice of the channels in the block INPUT MULTIPLEXERS they are

respectively connected to the input of the cavity controller and input of the cavity simulator. (compare chapter 11.2).

From the programming steering side, the *EXTERNAL* operation mode is considerably identical with the *INTERNAL* operation mode (compare chapter 3.2.1). Only in the case of the DAQ memory choice as an input generator, it requires programming with a set of signals (compare chapter 10.2.4). The memory module working as a generator **may not be used simultaneously** for data acquisition.

#### 3.2.4 STEP mode operation

In the *STEP* operation mode there are used the internal registers to control and read the results of the DSP processing from the block CAVITY SIMULATOR (see chapter 7.2.4) and the block CAVITY CONTRLLLER (see chapter 7.2.5). A single step is realized in the module *CIVITY STROBE STEP TIMER* in block TIMING CONTROLLER (see chapter 4.3.2).

The STEP operation mode is used for service purposes and tests, like emulation of vector content TSETPOINT\_I, TSETPOINT\_Q, TFEEDFORWARD\_I, TFEEDFORWARD\_Q and other ones. Due to this reason, the STEP operation mode may not be used in the real time.

For the servicing purposes, the access to the read registers of signals from the DSP processing of the cavity simulator and controller via the block COMMUNICATION CONTROLLER may be done in an arbitrary moment of time during the SIMCON system activity. It is recommended for the users to read from these registers after the operation step was completely done.

#### 4 TIMING CONTROLLER BLOCK DESCRIPTION

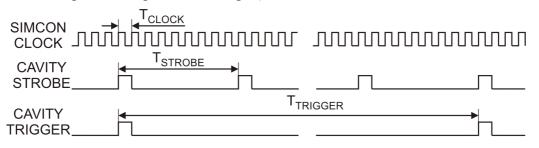

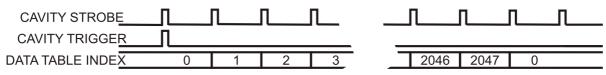

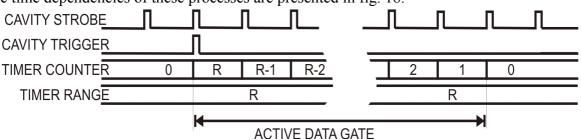

The block **TIMING CONTROLLER** processes and controls the timing signals distributed in the whole *SIMCON* system. It generates internal timing signals of the parameters set by program. The system has three basic clock signals. The time dependence between these signals were presented in fig. 8):

Fig. 8. Time dependencies between clock signals in the block TIMING CONTROLLER

- SIMCON CLOCK internal timing signal with the period  $T_{CLOCK}=25ns$  (40 MHz),

- *CAVITY STROBE* internal or external synchronizing signal for processing of the analog signals in the AD and DA converters with the period  $T_{STROBE} = l\mu s$  (*1 MHz*),

- *CAVITY TRIGGER* internal or external signal initializing the process of cavity control, now the period of this signal for FEL is  $T_{TRIGGER}=200ms$  (5 Hz) but may be changed on demand.

#### 4.1 Functional structure

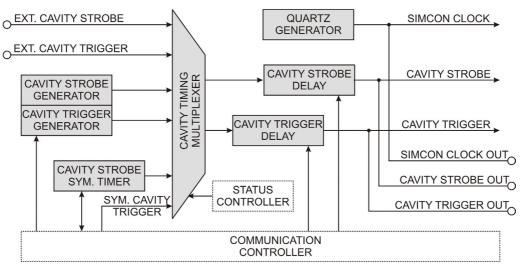

Fig. 8. Functional structure of the block TIMING CONTROLLER

The functional structure of the block **TIMING CONTROLLER** was presented in fig. 8. The are three processing layers in this structure:

- Choice of the clock signals, which are realized in the module CAVITY TIMING MULTIPLEXER,

- Generators of internal clock signals; the following modules create this structure: *CAVITY STROBE GENERATOR*, *CAVITY TRIGGER GENERATOR*, *CIVITY STROBE STEP TIMER*, *QUARTZ GENERATOR*,

• Timing adjustment consists of the following modules: CAVITY STROBE DELAY, CAVITY TRIGGER DELAY,

External signals *EXTERNAL CAVITY TRIGGER* and *EXTERNAL CAVITY STROBE* are output to the digital LEMO connectors. For the diagnostic and synchronization purposes with the external devices, the timing signals *SIMCON CLOCK OUT*, *CAVITY TRIGGER OUT* and *CAVITY STROBE OUT* were output to the digital LEMO connectors.

#### 4.2 Cavity timing multiplexer description

Choice of the source for clock signals is done automatically in accordance with the state of the register MODE\_OPER\_SEL. The register is situated in block STATUS CONTROLLER:

- For the operation modes of the system *MODE\_OPER\_INTERNAL* and *MODE\_OPER\_VECTOR* the clock signals are taken from the internal generators *CAVITY STROBE GENERATOR*, *CAVITY TRIGGER GENERATOR*,

- For the operation mode of the system *MODE\_OPER\_EXTERNAL*, there are taken external clock signals *EXTERNAL CAVITY TRIGGER* and *EXTERNAL CAVITY TRIGGER*. They are automatically synchronized with the signal *SIMCON CLOCK*,

- For the operation mode *MODE\_OPER\_STEP*, the clock signal is taken from internal generator *CIVITY STROBE SIMULATOR TIMER* and signal *SIMULATOR CIVITY TRIGGER*, which is programmed in block COMMUNICATION CONTROLLER.

#### 4.3 Programming description

The extent to program the block **TIMING CONTROL** includes setting the parameters of internal generators of clock signals and values of delays.

#### 4.3.1 Internal timing generation

The usage of internal clock signals requires a priori programming of the generator parameters *CAVITY STROBE GENERATOR* and *CAVITY TRIGGER GENERATOR*. To set the operation mode the following registers are used:

• For the *CAVITY STROBE GENERATOR* the signal period *CAVITY STROBE* is defined as a number of the periods of the signal *SIMCON CLOCK* (25 ns). The value of the rate diminished by 1 is stored in the signal register GENER\_STROBE\_RANGE. The period may be calculated using the following expression, where x is given parameter:

$$T_{STROBE} = T_{CLOCK} * (x+1) \Longrightarrow x = \frac{T_{STROBE}}{T_{CLOCK}} - 1,$$

The nominal range of register values is confined to 0 - 63. To obtain the period equal to  $1 \mu s$  from the signal *SIMCON CLOCK* (25 ns) it is necessary to set the value 39.

The implemented DSP algorithms allow to set the minimum value equal to 7. The sampling period is then *200ns*, or the modulated signal reaches *1.25 MHz*.

• For the *CAVITY TRIGGER GENERATOR* the signal period *CAVITY TRIGGER* is defined as a number of the signal periods *CAVITY STROBE*. The rate value diminished by *1* is stored in the signal register GENER\_TRIGGER\_RANGE. The period may be calculated using the following expression, where *y* is set parameter:

$$T_{TRIGGER} = T_{STROBE} * (y+1) = T_{CLOCK} * (x+1) * (y+1) \Longrightarrow y = \frac{T_{TRIGGER}}{T_{STROBE}} - 1 = \frac{T_{TRIGGER}}{T_{CLOCK} * (x+1)} - 1,$$

The nominal range of the values for the register is from 0 to 1048575 (0xFFFFF). To obtain the period 200  $\mu s$  from the signal *CAVITY STROBE* (1  $\mu s$ ) it is to input the value 199999, and the maximal period of the trigger signal is 1s.

#### 4.3.2 Step operation process

The operation mode *STEP OPERATION PROCESS* is a dedicated method of a computer aided DSP processes testing. The foundation of this operation mode is that the SIMCON system works in the real time during a strictly defined period of time. The time period is set as *REAL-TIME STEP PERIOD*. During the breaks in the processing, it is possible to do computer based reading of the DSP processing results and to set new input data for next DSP processes.

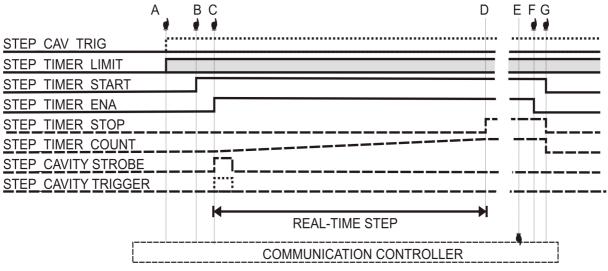

The step operation method is active when the state register MODE\_OPER\_SEL of the operation mode is set for *MODE\_OPER\_STEP*. The period *REAL-TIME STEP PERIOD* is generated in the module *CAIVITY STROBE STEP TIMER* according to the prior setting of the parameters. The module is triggered with the signal *SIMCON CLOCK*. The timing diagram *STEP OPERATON PROCESS* is presented in fig 21:

Fig. 9. Time diagram for the process STEP OPERATION

- A initialization of the global conditions of the process *STEP OPERATION* embraces setting of the following:

- register STEP\_TIMER\_LIMIT to the value equal to number of signal periods SIMCON CLOCK in the range from 0 to 63. The given data are diminished by 1, i.e. for the value 0 a single signal period for SIMCON CLOCK will be registered.

- register STEP\_CAV\_TRIG should be set to the appropriate value:

0: in the current step will not be generated STEP CAVITY TRIGGER,

1: in the current step will be generated STEP CAVITY TRIGGER.

- B initialization of the module *STEP TIMER* through setting STEP\_TIMER\_START=1.

- <u>C</u> activation of the module *STEP TIMER* through setting STEP\_TIMER\_ENA=1. From this very moment, the *STEP OPERATON PROCESS* is automatically triggered. The counter starts STEP\_TIMER\_COUNT which measures the time of the process.

- D automatic stop of the DAQ process after the counter STEP\_TIMER\_COUNT reaches a value set in the register STEP\_TIMER\_LIMIT. The following flag is set STEP\_TIMER\_STOP=1.

- E checking flag reading STEP\_TIMER\_STOP. Reading of value 0 means that STEP

*OPERATON PROCESS* continues. Reading the value *1* means that the process is finished. The flag reading may be done many times, waiting for the process to be finished.

- F stopping the work of the module *STEP TIMER* through setting STEP\_TIMER\_ENA=0.

- G introducing the module in the blocked state *STEP TIMER* through setting STEP\_TIMER\_START=0. The flag is deleted STEP\_TIMER\_STOP=0 and zeroing of STEP\_TIMER\_COUNT.

If the global acquisition conditions remain not changed, the next initialization of the DAQ process may disregard the stage A.

Temporary change in the flag state STEP\_DSP\_RESET from the value 0 to value 1 causes asynchronous resetting of the DSP processes in the cavity controller and simulator. For the servicing purposes of the flag state through the block COMMUNICATION CONTROLLER may be done in an arbitrary moment of the SIMCON system work. The SIMCON system users are strongly advised to reset the DSP processes only in the STEP MODE OPERATION just before doing the stage [A].

The flag state STEP\_DSP\_STOP=1 which means finishing of the calculation period for both DSP processes. For the servicing purposes of the flag state through the block COMMUNICATION CONTROLLER may be done in an arbitrary moment of the work state of SIMCON system. The users are strongly advised to reset the DSP processes only in the STEP MODE OPERATION just after doing the stages [E], [F] or [G].

#### 4.3.3 Time adjustment of the trigger signals

Time adjustments of the triggering signals is done by two modules:

- Module *CAVITY STROBE DELAY* delays the signal *CAVITY STROBE* of set number of signal periods *SIMCON CLOCK* (25 ns) in the range from 0 to 63. The value of delay is set in the register CAV\_STROBE\_DELAY. The range of delay embraces approximately 1.5  $\mu$ s, or exceeds a single period of signal *CAVITY STROBE*. Taking the value 0 means no additional delay of the signal *CAVITY STROBE*.

- Module *CAVITY TRIGGER DELAY* delays the signal *CAVITY TRIGGER* of set number of signal periods *CAVITY STROBE* ( $1 \mu s$ ) in the range from 0 to 2047. The value of delay is set in the register CAV\_TRIGGER\_DELAY. The range of delay embraces above 2 ms, or exceeds the longest control time of the cavity. Taking the value 0 means no additional delay of the signal *CAVITY TRIGGER*.

The signals *CAVITY STROBE* and *CAVITY TRIGGER* considered in the next part of this document are referenced **only** to the signals after the delay modules.

#### 5 INPUT PROCESSING BLOCK DESCRIPTION

The block **INPUT PROCESSING** provides proper conversion of values between a physical 14-bit resolution of the ADC converters and 18-bit resolution of the internal DSP processing, input signal calibration including amplification and regulated shift of constant voltage value, as well as initial smoothing of the input channels using a method of averaging of a set value of samples.

#### 5.1 Functional structure

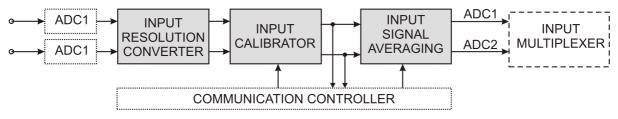

The block INPUT PROCESSING consists of an input module for resolution conversion *INPUT RESOLUTION CONVERTER, INPUT CALIBRATION* module and an averaging module *INPUT SIGNAL AVERAGING* for the input signal. Its functional structure is presented in fig. 10.

Fig. 10. Functional structure of the block INPUT PROCESSING

The module *INPUT RESOLUTION CONVERTER* realizes nondependently for each input channel the change from a *14*-bit U2 code obtained from particular ADC converter to *18*-bit representation of U2 code for the DSP processes. The conversion process relies on multiplication of the input signal value by the correction coefficient equal to *16*, what in such a case is equivalent to a logical shift of the input value to four places to the left.

The module of *INPUT CALIBRATOR* allows for fitting of the real input signal to the set levels of signals required in the algorithms of cavity simulator and controller. The module realizes, nondependently for each input channel a correction of the input signal. The performed process relies on the following DSP operation for each ADC channel in the 18-bit range:

$$y = x * G + O$$

where, the G parameter is the gain, the O parameter is constant voltage shift added to the signal.

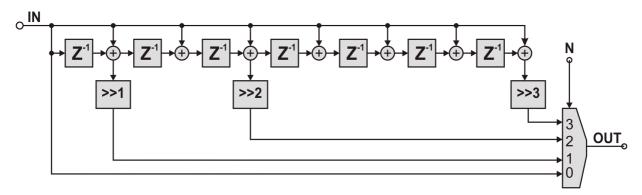

The module *INPUT SIGNAL AVERAGING* realizes nondependently for each input channel the following averaging functional operation:

$$Y_{AV}[K] = \frac{\sum_{t=0}^{K-1} x_{-t}}{K}$$

where:  $Y_{AV}[K]$  expresses the averaging value of the last K samples, or the current sample (time moment t=0), and the preceding samples, from t=(-1..-K+1) moments of time. The timing of the samples is defined by the signal *CAVITY STROBE*. The averaging coefficient K is set as:  $K=2^N$ , or for the range N=0..3, there are obtained the following values K=1,2,4,8.

Fig. 11. Time dependencies for cyclical data

For the value N=0 (K=1) work of the averaging circuit is confined for transmission of the input value to the output:  $Y_{AV}[1]=x_0$ . The structure of the averaging module is presented in fig.11.

#### 5.2 Programming description

Programming of the block INPUT PROCESSING relies on setting of calibration coefficients, the choice of a common, for both ADC channels, averaging coefficient.

The calibration parameters are determined by:

- For the channel ADC1, registers ADC1\_GAIN and ADC1\_OFFSET,

- For the channel ADC2, registers ADC2\_GAIN and ADC2\_OFFSET.

The choice the common averaging coefficient for both ADC channels is performed by writing to the register ADC\_AVER. The value of the averaging coefficient is in the range from 0 to 3. In order to dynamically change the parameters of the calibration one has to use the exchange registers (compare paragraph 7.2.3):

• for the channel ADC1 registers ADC1\_GAIN\_BUF and ADC1\_OFFSET\_BUF,

• for the channel ADC2 registers ADC2\_GAIN\_BUF and ADC2\_OFFSET\_BUF.

For the servicing purposes, the choice of the value for the averaging coefficient through the block COMMUNICATION CONTROLLER may be done during the arbitrary moment of the SIMCON system work time. The users of the SIMCON system are strongly advised to set the averaging coefficient choice register only during the SETUP MODE OPERATION.

The current state of the both ADC converters may be done through reading:

- For the channel ADC1, the register ADC1\_DATA,

- For the channel *ADC2*, the register ADC2\_DATA.

The following reading of the *ADC* channels are only for service purposes. It is to remember, that the read values may possess instable character, because they stem from the analog character of the input signals. The sampling period of the A/D converters results from the signal period *SIMCON CLOCK* and equals 25ns.

#### 6 OUTPUT PROCESSING BLOCK DESCRIPTION

The block **OUTPUT PROCESSING** provides proper value conversion between the physical 18-bit resolution of the internal DSP processing and 14-bit resolution of the DAC converters.

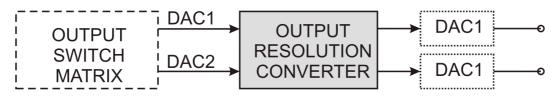

#### 6.1 Functional structure

The block OUTPUT PROCESSING consists only from the output module of resolution bits conversion *OUTPUT RESOLUTION CONVERTER*. Its functional structure was presented in figure 12.

Fig. 12. Functional structure of the block INPUT PROCESSING

The module *OUTPUT RESOLUTION CONVERTER* realizes, for each input channel, no dependently, the change of *18*-bit U2 code, used in the DSP processes, to *14*-bit representation NB required by the DA converters. The performed process relies on the dividing of the DSP signal value by the correction number equal to *16*, what in this case is equivalent to logical shift to the value to the left of 4 bits, and changing of the notation from U2 to NB.

#### 6.2 Programming description

The current version of the SIMCON system block OUTPUT PROCESSING does not require any programming and does not forward any results of its actions to the block COMMUNICATION CONTROLLER.

#### 7 PROGRAMMABLE DATA CONTROLLER

The block **PROGRAMMABLE DATA CONTROLLER** provides programming facility and data input to both DSP processes (for both cavity SIMULATOR and CONTROLLER) as well as data enabling control of the DSP processes. Three kinds of data are distinguished by the system:

- 1. *static data* they are input in the form of constant values (cavity parameters, controller parameters, like amplification coefficient of the cavity controller SGAIN\_I and SGAIN\_Q, see chapter s 1.2, 9.2),

- 2. *dynamic data* signal tables which are input in a form of a priori preprogrammed time dependent shape. Triggering of the beginning of the function is done by the signal *CAVITY TRIGGER*, and the next changes of these values are timed by the signal *CAVITY STROBE*. The example may be the values of tables TBEAM\_I and TBEAM\_Q of the cavity simulator (compare chapters 1.1, 8.2),

- 3. *control data* they are automatically generated in accordance with a priori set parameters and given in a form of periodic functions. The example may be values of I/Q modulator controller, which is described in the next chapter.

#### 7.1 Functional structure

Fig. 13. Functional structure of the block PROGRAMMABLE DATA CONTROLLER

The functional structure of the block **PROGRAMMABLE DATA CONTROLLER** was presented in fig. 13. The block provides separate mechanisms of data input to the both DSP blocks, depending on the data type:

- Only the static type data are provided directly from the block registers of COMMUNICATION CONTROLLER. Each register is 18-bit. During the real time work it is possible to change the values of respective control register of the DSP process. A priori, the alternative registers are programmed and the request for change is performer. The change is done automatically before the cavity process starts.

- For the dynamic data, the module *INDEX COUNTER* calculates the current address of the cells *SWITCHED DATA MEMORY*. From the moment of signal trigger *CAVITY TRIGGER*, the successive cells in the memory table are input to the particular DSP process. The change of index has a periodic nature from 0 to 2047, till the next value of 0. The signal *CAVITY STROBE* means next steps of the process. The time dependencies of this process were shown in fig. 15.

| CAVITY STROBE   |     | л | л | Π | Л   | Л | Π | Л | л |

|-----------------|-----|---|---|---|-----|---|---|---|---|

| CAVITY TRIGGER  |     | Л |   |   |     |   |   |   |   |

| GENERATOR VALUE | ?   | 2 | 3 | 0 | 1   | 2 | 3 | 0 | 1 |

| GENERATOR INIT  | S=2 |   |   |   | S=2 |   |   |   |   |

Fig. 14. Time dependencies for cyclic data.

The dynamic data are remembered in a form of tables of the dimensions 18-bits for 2048 cells. In this way, the change dynamics is provided for  $l\mu s$  for the period of time  $2048\mu s$ , which embraces the whole period of cavity control by the controller.

During the real time work it is possible to change the values of tables by earlier programming of alternative tables and setting the request for change. The change is done automatically before the cavity control process begins (compare chapter 7.2.3).

The choice of data of dynamic or static type (variant advice only in the *STEP MODE OPERATION*) is done through the control of the module *DATA MUX*.

• Control data for the modulation are generated with the aid of a cyclic generator working in the range from 0 to 3 in the module *DRIVER MODULATOR*. The signal *CAVITY TRIGGER* initializes cyclic generator to the *initial value (S)*, but the change of his value is triggered by the signal *CAVITY STROBE*. The time dependencies were shown in fig. 14 for the initializing value S=2.

Fig. 15. Time dependencies for dynamic data

#### 7.2 Programming description

The programming of the block **PROGRAMMABLE DATA CONTROLLER** relies on the input of static data (writing of 18-bit register) and dynamic data (filling the memory areas of 2048 cells 18-bit each) and on the choice of the channel in the module *DATA MUX*. The details of programming of particular components are described in the chapters below.

#### 7.2.1 Dynamic data multiplexer

The multiplexer *DATA MUX* controls the choice of data kind, in dependence on the values of flags CTRL\_PROC\_REQ and SIM\_PROC\_REQ (compare paragraph 3.2):

- CTRL\_PROC\_REQ=0 chooses channel 0 for all static data of block CAVITY CONTROLLER (compare paragraph 7.2.5),

- SIM\_PROC\_REQ=0 chooses channel 0 for all static data block CAVITY SIMULATOR (compare paragraph 7.2.4),

- CTRL\_PROC\_REQ=1 chooses channel *1* for all dynamic data block CAVITY CONTROLLER (compare paragraph 7.2.5),

- SIM\_PROC\_REQ=1 chooses channel *l* for all dynamic data block CAVITY SIMULATOR (compare paragraph 7.2.4),

#### 7.2.2 Modulator driver

The module *MODULATOR DRIVER* requires programming of the initial value in the register VM\_DRV\_START in the range from 0 to 3.

Physical writing of the value VM\_DRV\_START to the module *MODULATOR DRIVER* is done through performing write operation of an arbitrary value to the register VM\_DRV\_COUNT.

For the servicing purposes, there is a possibility to read the current value of the module *MODULATOR DRIVER* via the register VM\_DRV\_COUNT. This value has, however, a nonstable character, because it changes periodically in the range from 0 to 3 every  $1\mu s$ . The stable value is obtained in the *STEP MODE OPERATON* or *SETUP MODE OPERATON*.

#### 7.2.3 Data switching

The request to change the static and dynamic data relies on the negation of the actual flag state TAB\_SWITCH\_REQ, i.e. changing its value from 0 to 1 or vice versa. The acknowledgement of the change causes copying of the new value to TAB\_SWITCH\_ACK.

The change of registers and memory is started by signal *CAVITY TRIGGER* in an automatic way, simultaneously for all of the following components:

- ADC1\_GAIN with ADC1\_GAIN\_BUF and ADC1\_OFFSET with ADC1\_OFFSET\_BUF,

- ADC2\_GAIN with ADC2\_GAIN\_BUF and ADC2\_OFFSET with ADC2\_OFFSET\_BUF,

- CAL1 with CAL1\_BUF and CAL2 with CAL2\_BUF,

- TSETPOINT\_I with DAQ1 and TSETPOINT\_Q with DAQ2,

- TFEEDFORWARD\_I with DAQ3 and TFEEDFORWARD\_Q with DAQ4,

- TGAIN\_I with TBEAM\_I and TGAIN\_Q with TBEAM\_Q.

Till the moment to obtain the acknowledgment TAB\_SWITCH\_ACK it is necessary not to change the value of TAB\_SWITCH\_REQ.

#### 7.2.4 Cavity simulator programmable data packet

The block CAVITY SIMULATOR, in accordance with the algorithm described in chapter 1.1 requires setting of the following data:

- *BEAM* (dynamic data): is represented by a table TBEAM\_I and TBEAM\_Q or alternatively by the registers SBEAM\_I and SBEAM\_Q,

- *ROTATION MATRIX* [C] (static data):  $C = \begin{bmatrix} c_1 \\ c_2 \end{bmatrix}$  are expressed in succession by the parameters CAL1 and CAL2 (exchange registers: CAL1 BUF, CAL2 BUF),.

parameters one r and onez (exchange registers. One r\_bor, onez\_bor),.

- MATRIX\_A1\_21 and MATRIX\_A1\_22 individual coefficients of the matrix [A1],

- *MATRIXES* [A<sub>1</sub>], [A<sub>2</sub>], [A<sub>3</sub>] (static data):  $A_{n=1,2,3} = \begin{bmatrix} 1 & a_{12} \\ a_{21} & a_{22} \end{bmatrix}$  are expressed by the following

parameters:

- MATRIX\_A12 common coefficient  $a_{12}$  for all three matrixes,

- $\circ$  MATRIX\_A1\_21 and MATRIX\_A1\_22 individual coefficients of the matrix [A<sub>1</sub>],

- $\circ$  MATRIX\_A2\_21 and MATRIX\_A2\_22 individual coefficients of the matrix [A<sub>2</sub>],

- MATRIX\_A3\_21 and MATRIX\_A3\_22 individual coefficients of the matrix [A<sub>3</sub>],

- *MATRIXES* [*B*<sub>1</sub>], [*B*<sub>2</sub>], [*B*<sub>3</sub>] (static data):  $B_{n=1,2,3} = \begin{bmatrix} b_1 & 0 \end{bmatrix}$  the are expressed by the following parameters  $b_1$  appropriately for the successive matrixes: MATRIX\_B1\_1, MATRIX\_B2\_1 and MATRIX\_B3\_1,

- COEFFICIENT "H" (static data): is expressed by the PARAM\_H,

- *COEFFICIENT* ,, *P*" (static data): is expressed by the PARAM\_P,

- flag SIM\_MODE (static data) sets the dynamic range of the cavity voltage simulation:

- the value 0: 16MV/m,

- the value 1: 32MV/m.

- Activation of the static register requires setting SIM\_PROC\_REQ=0, alternatively switching on the set point tables SIM\_PROC\_REQ=1 (compare paragraph 3.2).

#### 7.2.5 Cavity controller programmable data packet

The block CAVITY CONTROLLER, in agreement with the algorithm described in the chapter 1.2 requires setting the following data CTRL\_PROC\_REQ=0:

- *SET POINT* (dynamic data): is represented by the tables TSETPOINT\_I and TSETPOINT\_Q or alternatively by the registers SSETPOINT\_I and SSETPOINT\_Q,

- *FEED FORWARD* (dynamic data): is represented by the tables TFEEDFORWARD\_I and TFEEDFORWARD\_Q or alternatively by the registers SFEEDFORWARD\_I and SFEEDFORWARD\_Q,

- *GAIN* (dynamic data): is represented by the tables TGAIN\_I and TGAIN\_Q or alternatively by the registers SGAIN\_I and SGAIN\_Q, $\$

- *COMP1* .. *COMP4* (static data): is represented by the registers COMP1 .. COMP4. (swap registers: COMP1\_BUF .. COMP4\_BUF)

Activation of the static registers requires setting CTRL\_PROC\_REQ=0 or alternatively switching on the set point tables CTRL\_PROC\_REQ=1 (compare paragraphs 3.2).

#### 8 CAVITY SIMULATOR BLOCK DESCRIPTION

The block CAVITY SIMULATOR performs, in the real time, the algorithm of the superconducting cavity behavior, in agreement with the requirements of the LLRF system (see chapter 1.1). An 18-bit fixed point algorithm was implemented with the use of the DSP components present in the FPGA chip Xilinx VirtexII-V3000.

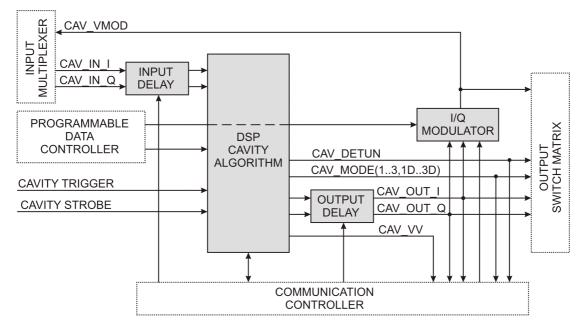

#### 8.1 Functional structure

The block CAVITY SIMULATOR consists of the synchronous numerical processing module *DSP CAVITY ALGORITHM*, from the modules of signal delays *INPUT DELAY* and *OUTPUT DELAY* and from the modulator module of I/Q *MODULATOR*. Its functional structure was presented in figure 16.

Fig. 16. Functional structure of the block CAVITY SIMULATOR

The module DSP CAVITY ALGORITHM processes the signal vector for cavity control  $CAV_{IN}I$  and  $CAV_{IN}Q$ , which is provided from the block INPUT MULTIPLEXER (see chapter 11) in accordance with the parameters provided from the block PROGRAMMABLE DATA CONTROLLER (see chapter 5). There are the following signals obtained at the output of this block:

- Basic signals from the cavity (*CAV\_OUT\_I* and *CAV\_OUT\_Q*),

- Modulated signal I/Q (CAV\_VMOD),

- Detuning signal from the cavity mechanical model (CAV\_DETUN),

- Six signals of the state vector [W] of the mechanical model (*CAV MODE(1..3, 1D..3D*)).

- Signal of the square value for the high power EM field gradient  $v^2$  (CAV\_VV),

The module *I/Q MODULATOR* realizes modulation process for the signals I and Q from the cavity. The modulator control is provided by the module *MODULATOR DRIVER* situated in the block PROGRAMMABLE DATA CONTROLLER (see chapter 7.1).

The modules of delay of the input and output DSP data (*INPUT DELAY* and *OUTPUT DELAY*) allow to simulate the physical delays introduced by the transmission lines

(waveguides). A single step of the delay defines the timing of the signal *CAVITY STROBE*, which is currently equal to  $l\mu s$ .

#### 8.2 Programming description

The programming of the work of the block CAVITY CONTROLLER relies on:

- Setting of proper parameters in the block PROGRAMMABLE DATA CONTROLLER (see chapter 7.2.5). These are the following parameters: *BEAM*, matrixes [*A*<sub>1</sub>], [*A*<sub>2</sub>], [*A*<sub>3</sub>], [*B*<sub>1</sub>], [*B*<sub>2</sub>], [*B*<sub>3</sub>], coefficients ,,*H*" and ,,*P*",

- Setting of the modulation phase realized in the module *I/Q MODULATOR* in reference to the demodulation realized in the cavity controller (compare chapter 7.1 and 7.2.2). The phase change is determined by the register VM\_DRV\_OFFSET in the value range of 0 3,

- Setting of the delays for the input and output signals, respectively via the programming of the registers CAV\_DELAY\_IN and CAV\_DELAY\_OUT. Each of the registers allows to write the values from 0 to 15. In this way, the range of delays is provided up to  $15\mu s$  with a step of  $1\mu s$ . Setting the value of 0 means no additional delay introduced.

In the operation mode *STEP OPERATON PROCESS* the following registers are made available for computer based writing via the block COMMUNICATION CONTROLLER. The registers have the same eigen-names with the source signals for the cavity simulator DSP processing:

• registers CAV\_IN\_I and CAV\_IN\_Q controlling directly the signals CAV\_IN\_I and CAV\_IN\_Q.

In the operation mode *STEP OPERATON PROCESS*, for the computer based reading, via the block COMMUNICATION CONTROLLER, there are made available the following current values of the cavity simulator DSP processing results, via the registers with the eigennames equal to the relevant signals:

- signals *CAV\_OUT\_I* and *CAV\_OUT\_Q* respectively through the registers CAV\_OUT\_I and CAV\_OUT\_Q,

- signal CAV VMOD via the register CAV\_VMOD,

- signal CAV DETUN via the register CAV\_DETUN,

- six signals of mechanical modes *CAV\_MODE(1..3, 1D..3D)* via the registers:

- CAV MODE1 the first mechanical mode is accessible in the register CAV\_MODE1,

- $\circ$  *CAV\_MODE1D* derivative of the first mechanical mode is accessible via the register CAV\_MODE1D,

- CAV MODE2 the second mechanical mode is accessible in the register CAV\_MODE2,

- *CAV\_MODE2D* derivative of the second mechanical mode is accessible via the register CAV\_MODE2D,

- CAV MODE3 the third mechanical mode is accessible via the register CAV\_MODE3,

- *CAV\_MODE3D* derivative of the third mechanical mode is accessible via the register CAV\_MODE3D.

- The signal *CAV\_VV* via the register CAV\_VV,

For the servicing purposes, the access to the read registers of the signals from the cavity simulator DSP process, via the COMMUNICATION CONTROLLER, may be done in the arbitrary moment during the work time of the SIMCON system. The users are strongly recommended to read these registers only during the SETUP MODE OPERATION.

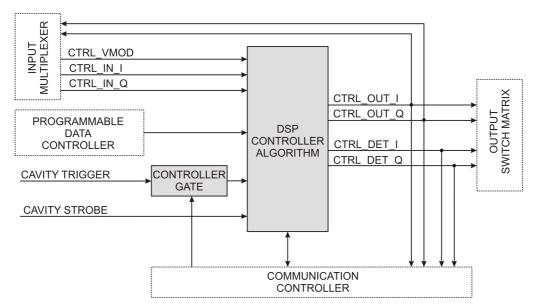

#### 9 CAVITY CONTROLLER BLOCK DESCRIPTION

The block CAVITY CONTROLLER performs, in the real time, a control algorithm for the superconductive cavity, in agreement with the requirements of the LLRF system design parameters (compare chapter 1.2). There was implemented an 18-bit fixed point algorithm, with the usage of the DSP components integrated into the FPGA Xilinx VirtexII-V3000 chip.

#### 9.1 Functional structure

The block CAVITY CONTROLLER consists firm the synchronous module of numerical processing (*DSP CONTROLLER ALGORITHM*) and from synchronization module of I/Q detection (*DRIVER MODULATOR*). Its functional structure was presented in figure 17.

Fig. 17. Functional structure of the block CAVITY CONTROLLER

The module *DSP CONTROLLER ALGORITHM* processes the appropriate modulated input signals provided from the block INPUT MULTIPLEXER (see chapter 11) in accordance with the parameters provided by the block **PROGRAMMABLE DATA** CONTROLLER (see chapter 5). The output of the module gives two output vectors:

- Basic control signal for vector modulator of the klystron (CTRL I, CTRL Q),

- Auxiliary signal after the detection (CTRL\_DET\_I, CTRL\_DET\_Q)

The module *CONTROLLER GATE* allows to activate the block CAVITY CONTROLLER only during the active state of the time gate, and during the rest of time the output data from the block have 0 value. The signal *CAVITY TRIGGER* initializes the gate for a set period of time by the *time range (R)*. The gate is timed with the signal *CAVITY STROBE*. The time dependencies of these processes are presented in fig. 18.

Fig. 18. Time dependencies of signals for the time gate of the cavity controller

#### 9.2 Programming description

The programming of the block CAVITY CONTROLLER relies on:

- Setting of appropriate parameters in the block **PROGRAMMABLE DATA CONTROLLER** (see chapter 7.2.3). These are the following parameters: *SET POINT*, *FEED FORWARD* and *GAIN*.

- Setting of the choice variant for control signals through the value CTRL\_IQ\_MODE:

- 0: choice of modulated signal CTRL\_VMOD,

- 1: choice of pair of signals CTRL\_IN\_I and CTRL\_IN\_Q

- setting of activity time for the time gate in the register CTRL\_ACTIVE in the range from *1* to 2047 periods of the signal *CAVITY STROBE* (or nominally every *1µs*).

Setting the value to 0 in the register CTRL\_ACTIVE is reserved only to the servicing purposes – it keeps the gate active all the time, or the cavity controller DSP process is all the time zeroed.

In the operation mode *STEP OPERATON PROCESS*, for the computer reading, via the block **COMMUNICATION CONTROLLER**, the following register is made available with the name identical as the cavity controller DSP processing source signal:

• register CTRL\_VMOD controlling directly the signal *CTRL\_VMOD*.

In the operation mode *STEP OPERATON PROCESS*, for the computer reading, via the block COMMUNICATION CONTROLLER, the following current values of the DSP processing are made accessible, via the registers of the names identical as the cavity controller DSP signals:

- signals  $CTRL_I$  and  $CTRL_Q$  respectively through the registers CTRL\_OUT\_I and CTRL\_OUT\_Q,

- signals *CTRL\_DET\_I* and *CTRL\_DET\_Q* respectively through the registers CTRL\_DET\_I and CTRL\_DET\_Q,

For the servicing purposes, the access to the reading registers of the cavity controller DSP process signals is available, via the block COMMUNICATION CONTROLLER. The access may be done during the arbitrary moment of the SIMCON system activity. The SIMCON users are strongly recommended to read these data from these registers only during the SETUP MODE OPERATION.

#### 10 DATA ACQUISITION (DAQ) BLOCK DESCRIPTION

The block DATA ACQUISITION (DAQ) allows for current monitoring of the most important signals in the system. These may be input signals, as well as output, internal results from the DSP processing in the algorithms of the cavity simulator and controller. It may additionally fulfill the function of a programmable signal generator for tests of input and output signals.

#### 10.1 Functional structure

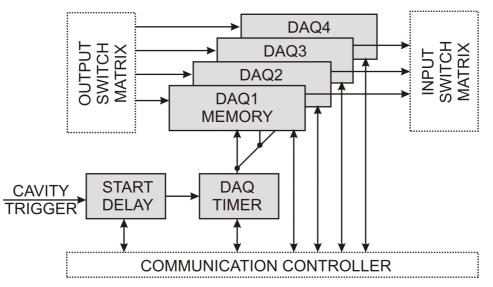

The block DAQ realizes parallel, synchronized registration of four data streams. Its functional structure is presented in figure 19.

Fig. 19. Functional structure of the block DATA ACQUISITION

The choice of the source data streams is done in the block OUTPUT SWITCH MATRIX. The block DAQ bases on four memory modules. Each memory (DAQ1 .. DAQ4) has 2048 words per 18-bits each. The acquisition process is controlled by the DAQ TIMER, in agreement with the a priori set parameters. Triggering of the acquisition process is done by the signal CAVITY TRIGGER. This signal may be delayed in the module START DELAY of a preset number of clock signals CAVITY STROBE (1 MHz). In this way, one obtains the possibility to shift the reading time window in relation to the trigger signal, with the step of  $l\mu s$ .

Additionally, the block DAQ realizes the functions of programmable input test vectors in the operation mode *VECTOR\_OPERATION*. The data from the memory DAQ1 .. DAQ3 are transmitted via the block INPUT MULTIPLEXERS respectively to a single input of the cavity controller and to two inputs of the cavity simulator.

#### 10.2 Programming description

The programming of the block DATA ACQUISITION allows to set operation modes, for direct access to the memory areas, programming the conditions of the acquisition in the real time and control of the status of the data acquisition process.

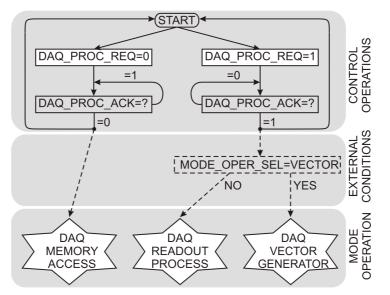

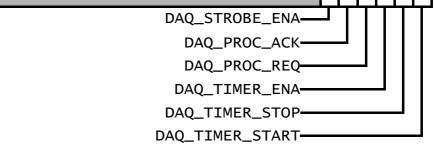

#### **10.2.1 DAQ modes control**

The basic operation modes of the DAQ block are set with the flag DAQ\_PROC\_REQ.

Fig. 20. Flow diagram for the choice of the operation mode of the DAQ block.

Acknowledgement of the required operation mode is obtained by reading of the identical logical state of the flag DAQ\_PROC\_ACK. Till the time, both flags have the same states, the DAQ block is in the state of switching and has no defined state. The block DAQ may be set in one of three different operation modes, what was presented in fig. 20. The choice of the operation mode in the real time is forced by the current state of the register MODE\_OPER\_SEL. The particular operation modes are described in details in the next sub-chapters.

#### 10.2.2 DAQ memory access

For the flag value DAQ\_PROC\_REQ=0 (and acknowledgement via setting of the value of flag DAQ\_PROC\_ACK=0) the direct access to the memory DAQ1..*DAQ4* is obtained in the write or read mode. The base addresses are determined by the parameters DAQ1..DAQ4\_MEM. Each memory represents a continuous area of 2048 relative address positions counted from the value of 0 till 2047 and including 18-bit words.

#### **10.2.3 DAQ readout process**

The operation mode *DAQ\_READOUT\_PROCESS* is obtained after programming the value of the flag DAQ\_PROC\_REQ=1 (confirmed by setting the value of the flag DAQ\_PROC\_ACK=1) and after fulfilling the condition, that no operation mode *OPER MODE VECTOR* was programmed for the system in the register MODE\_OPER\_SEL.

Fig. 21. Time diagram of the data acquisition process in the block DAQ

The debated operation mode allows for parallel data acquisition of four data streams. It is performed automatically, according to the a priori preset parameters. The key stages of the control process for the data acquisition are presented in figure 21:

- A initialization of the global parameters for the acquisition process embraces setting of the following parameters:

- flag DAQ\_STROBE\_ENA respectively to the value:

0: data will be registered with the speed of the system clock 40MHz (every 25ns),

1:data will be registered with the speed of the FEL clock 1MHz (every 1µs)

- register DAQ\_TIMER\_LIMIT to the value of successive number of data registered in the DAQ memories in the range of from 0 to 2047. The set values are diminished by 1, i.e. for the value 0 the registration of a single data is done.

- register DAQ\_ DELAY to the value of signal delay CAVITY TRIGGER. The delay means the number of clock signals of *1MHz*, or a single step is *1µs*. Assuming the value of 0 means no additional delay for the signal CAVITY TRIGGER.

- B module initialization *DAQ TIMER* via setting DAQ\_TIMER\_START=1.

- C module activation *DAQ TIMER* via setting DAQ\_TIMER\_ENA=1. From this moment on, the block waits for the signal *CAVITY TRIGGER*, which synchronously triggers the data acquisition process.

- D automatic triggering of the delay process for the signal *CAVITY TRIGGER*. The delay value is determined by the value of the register DAQ\_DELAY

- E automatic triggering of the data acquisition process delayed by the signal *CAVITY TRIGGER*. The counter starts DAQ\_TIMER\_COUNT which counts the amount of the registered data.

- F automatic ending of the data acquisition process, after the counter DAQ\_TIMER\_COUNT reaches the value set in the register DAQ\_TIMER\_LIMIT. The flag is set DAQ\_TIMER\_STOP=1.

- G checking reading of the flag value DAQ\_TIMER\_STOP. Reading of the value  $\theta$  means, that the data reading process still lasts. Reading the value *I* means, that the DAQ process was finished. Reading of the flag state may be done many times, waiting for the end moment of the DAQ process.

- H stopping of the work of the module *DAQ TIMER* via setting DAQ\_TIMER\_ENA=0.

- I introduction of the module in the blocked state *DAQ TIMER* via setting DAQ\_TIMER\_START=0. The flag is deleted DAQ\_TIMER\_STOP=0. In this operation mode of the *DAQ TIMER* it is possible to switch the operation modes of the block DAQ, for example to read the contents of the memories DAQ1..*DAQ4* during operation mode *DAQ\_MEMORY\_ACCESS* (see chapter 10.2.2).

If the global DAQ conditions remain unchanged, at the next initialization of the DAQ process, the stage A may be omitted.

#### **10.2.4 DAQ vector generator**

The work in operation mode *DAQ\_VECTOR\_GENERATOR* relies on periodic generation of the of the memory contents DAQ1.. DAQ3 synchronously with the signal *CAVITY TRIGGER*. In the operational sense, the generators are acting identically as *CONTROL\_DATA\_TABLES*. It requires only previous data loading in the operation mode *DAQ\_MEMORY\_ACCESS* (see chapter 10.2.2).

The operation mode *DAQ\_VECTOR\_GENERATOR* is now in the testing period.

#### 11 INPUT MULTIPLEXERS BLOCK DESCRIPTION

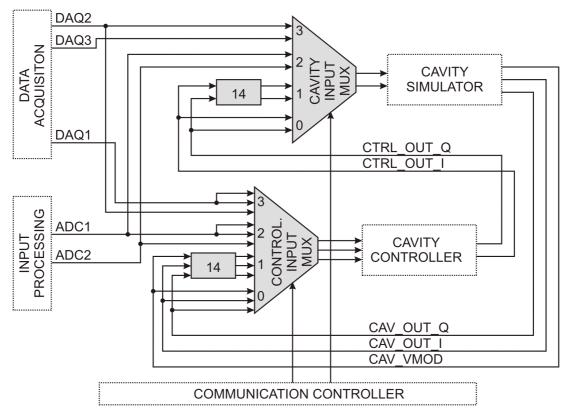

The input multiplexers allow for nondependent programmable choice of the input control signals for the blocks CAVITY SIMULATOR and CAVITY CONTROLLER. Choice of the multiplexer input signals provides the realization of the feedbacks (external analog, internal digital) between the DSP blocks and nondependent control of the particular DSP blocks (external analog, internal testing digital).

#### 11.1 Functional structure

The block INPUT MULTIPLEXERS provides simultaneous choice of the two input signals for the block CAVITY SIMULTOR and a single signal for the block CAVITY CONTROLLER. Both multiplexers have 4 variants for the choice of the inputs. The functional structure of the block INPUT MULTIPLEXERS was presented in figure 22.

Fig. 22. Functional structure of the block INPUT MULTIPLEXERS

For each of the multiplexers, the following types of the input signals are distinguished:

- *channel 0*: realization of full resolution (18-bit) of the digital feedback between the DSP blocks of the cavity controller and simulator,

- *channel 1*: digital simulation of the analog (14-bit) feedback, respectively between the DSP blocks of cavity controller and simulator, simulating the resolution of the AD and DA converters,

- *channel 2*: connection of respective signals from the AD converters from blocks DAC1 and DAC2,

- *channel 3*: connection of blocks DAQ1..DAQ3 with the choice of the VECTOR operation mode (see chapter 0) or zeroing the inputs for the rest of the operation modes.

#### 11.2 Programming description

The choice of the source channel (compare figure 19) is done for each multiplexer nondependently. The number of the chosen channel in the range of from 0 to 3 is programmed in the block COMMUNICATION CONTROLLER:

- For the module CAVITY INPUT MUX in the register MUX\_IN\_CAVITY

- For the module CONTROLLER INPUT MUX in the register MUX\_IN\_CONTRL

For the servicing purposes the choice of the active multiplexer channel, via the block COMMUNICATION CONTROLLER may be done during an arbitrary moment of the SIMCON activity. The users are strongly recommended to set the registers only during the SETUP MODE OPERATION.

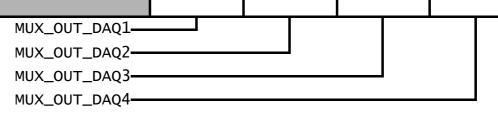

#### 12 OUTPUT SWITCH MATRIX BLOCK DESCRIPTION

The switching matrix realized in the block OUTPUT SWITCH MATRIX allows for nondependent programmable choice of the output signals from the blocks PROGRAMMABLE DATA CONTROLLER, CAVITY SIMULTOR, CAVITY CONTROLLER, ADC1 and ADC 2 and from the module *TEST GENERATOR* to the inputs of the blocks DAQ1..4 and DAC1..2. The choice possibility for input signals of multiplexers provides realization of monitoring of particular signals and choice of signals output in the analog form from the SIMCON system to the outer world, via the DAC converters.

#### 12.1 Functional structure

The block OUTPUT SWITCH MATRIX is a switching matrix of 23 inputs to 6 outputs. It enables a simultaneous choice of the output signals for four DAQ blocks and for two DAC channels. All 23 input signals may be nondependently connected to each output. The functional structure of the block OUTPUT SWITCH MATRIX is presented in figure 23.

The module TEST GENERATOR generates a rising saw-like signal initialized by the

Fig. 23. Functional structure of the block INPUT MULTIPLEXERS

signal *CAVITY TRIGGER*. The initialization of the generator causes its setting to 0 value and next each clock of the signal *SIMCON CLOCK* increases this value by 1. The generator gives 18-bit values in a periodic way.

For each input channel there are distinguished the following kinds of the input signals of 18-bit in resolution:

- channel 0: test signal from module TEST GENERATOR,

- *channel 1*: external signal *CAV\_OUT\_I* (compare chapter 8.1),

- *channel 2*: internal signal *CAV\_OUT\_Q* (compare chapter 8.1),

- *channel 3*: internal signal *CAV\_DETUN* (compare chapter 8.1),

- *channel 4*: internal signal *CAV\_VMOD* (see chapter 8.1),

- *channel 5*: internal signal *CTRL\_DET\_I* (compare chapter9.1),

- *channel 6*: internal signal *CTRL\_DET\_Q* (compare chapter9.1),

- *channel* 7: internal signal *CTRL\_I* (compare chapter9.1),

- *channel* 8: internal signal *CTRL\_Q* (compare chapter9.1),

- channel 9: internal signal TGAIN I (compare chapter7.1),

- *channel 10:* internal signal *TGAIN\_Q* (compare chapter7.1),

- channel 11: internal signal TSETPOINT\_I (compare chapter7.1),

- *channel 12*: internal signal *TSETPOINT\_Q* (compare chapter7.1),

- *channel13* : internal signal *TFEEDFORWARD*\_*I* (compare chapter7.1),

- channel 14: internal signal TFEEDFORWARD \_Q (compare chapter7.1),

- *channel 15*: internal signal *TBEAM*\_*I* (compare chapter7.1),

- *channel 16*: internal signal *TBEAM \_Q* (compare chapter7.1),

- channel 17: internal signal CAV\_MODE1 (compare chapter 8.1),

- channel 18: internal signal CAV\_MODE1D (compare chapter 8.1),

- channel 19: internal signal CAV\_MODE2 (compare chapter 8.1),

- channel 20: internal signal CAV\_MODE2D (compare chapter 8.1),

- *channel 21*: internal signal *CAV MODE3* (compare chapter 8.1),

- channel 22: internal signal CAV\_MODE3D (compare chapter 8.1),

- channel 23: input signal ADC1 (compare chapter5.1),

- channel 24: input signal ADC2 (compare chapter5.1),

#### 12.2 Programming description

The choice of the source channel (compare figure 19) is done for each output of the switching matrix nondependently. The number of the input channel in the range of from 0 to 22 is programmed in the block COMMUNICATION CONTROLLER:

- for the block DAQ1 for the register MUX\_OUT\_DAQ1,

- for the block DAQ2 for the register MUX\_OUT\_DAQ2,

- for the block DAQ3 for the register MUX\_OUT\_DAQ3,

- for the block DAQ4 for the register MUX\_OUT\_DAQ4,

- for the block DAC1 for the register MUX\_OUT\_DAC1,

- for the block DAC2 for the register MUX\_OUT\_DAC2.

The choice of improper channels numbers from the range 23-31 automatically switches the channel 0. The users are strongly advised not to set the improper channel values.

For the servicing purposes, the choice of the active channels via the block COMMUNICATION CONTROLLER may be done during an arbitrary moment of the SIMCON activity. The users are strongly advised to set the choice for the multiplexer channel numbers only during the *SETUP MODE OPERATION*.

# 13 PROGRAMMABLE I/O SPECIFICATION

This chapter presents the specification for the I/O space of the SIMCON system, which is made accessible for the priority computer control via the block COMMUNICATION CONTROLLER.

#### 13.1 I/O specification list by addresses

# CHECKSUM (0000H)

31|30|29|28|27|26|25|24|23|22|21|20|19|18|17|16|15|14|13|12|11|10| 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 CHECKSUM

CHECKSUM (RO) – contains constant hexadecimal control value: 0028BD94H.

#### CREATOR (0001H)

31|30|29|28|27|26|25|24|23|22|21|20|19|18|17|16|15|14|13|12|11|10| 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 CREATOR

CREATOR (RO) – contains constant ASCII symbol which identifies the constructor (group "*ELHEP-WARSAW*"): "EHWA", what in the hexadecimal reading means the value: 45485741H.

#### IDENTIFIER (0002H)

31|30|29|28|27|26|25|24|23|22|21|20|19|18|17|16|15|14|13|12|11|10| 9| 8| 7| 6| 5| 4| 3| 2| 1| 0 IDENTIFIER

IDENTIFIER (RO) – contains constant ASCII symbol identifying the system: "SIMC", what in the case of hexadecimal reading means: 53494D43H.

#### VERSION (0003H)

# 313029282726252423222120191817161514131211109876543210 MAIN\_VERSION SUB\_VERSION REV\_VERSION

Packet VERSION – contains constant identifier of the version expressed hexadecimally:

- MAIN\_VERSION (RO): contains value 02H,

- SUB\_VERSION (RO): contains value 01H,

- REV\_VERSION (RO): contains value 0001H.

- •

# USER\_REG1 (0004H)

#### 31|30|29|28|27|26|25|24|23|22|21|20|19|18|17|16|15|14|13|12|11|10| 9| 8| 7| 6| 5| 4| 3| 2| 1| 0 USER\_REG1

USER\_REG1 (RW) – control-test register designed solely for the user.

# USER\_REG2 (0005H)

31|30|29|28|27|26|25|24|23|22|21|20|19|18|17|16|15|14|13|12|11|10| 9| 8| 7| 6| 5| 4| 3| 2| 1| 0 USER\_REG2

$USER_REG2$  (RW) – control-test register designed solely for the user.

# STATUS (0006H)

313029282726252423222120191817161514131211109876545432

Packet STATUS contains global components of the control of SIMCON system:

- MODE\_OPER\_SEL (RW): see chapter 3.2,

- CTRL\_PROC\_REQ (RW): see chapter 3.2,

- CTRL\_PROC\_ACK (R): see chapter 3.2,

- SIM\_PROC\_REQ (RW): see chapter 3.2,

- SIM\_PROC\_ACK (R): see chapter 3.2,

- SIM\_MODE (RW): see chapter 3.2,